# SISTEMA PLC DE BANDA ANGOSTA PARA LA CARACTERIZACIÓN DE LA IMPEDANCIA DE LA RED ELÉCTRICA

#### Adrián de la Fuente

El presente Trabajo de Tesis ha sido desarrollado en el Laboratorio de Instrumentación y Control de la Universidad Nacional de Mar del Plata, y presentado al Departamento de Electrónica de la Facultad de Ingeniería de la Universidad Nacional de Mar del Plata el 12 de Noviembre de 2018, como requisito parcial para la obtención del título de Ingeniero Electrónico.

Director: Dr. Ing. Matías Hadad

Codirector: Dr. Ing. Marcos Funes

RINFI se desarrolla en forma conjunta entre el INTEMA y la Biblioteca de la Facultad de Ingeniería de la Universidad Nacional de Mar del Plata.

Tiene como objetivo recopilar, organizar, gestionar, difundir y preservar documentos digitales en Ingeniería, Ciencia y Tecnología de Materiales y Ciencias Afines.

A través del Acceso Abierto, se pretende aumentar la visibilidad y el impacto de los resultados de la investigación, asumiendo las políticas y cumpliendo con los protocolos y estándares internacionales para la interoperabilidad entre repositorios

Esta obra está bajo una Licencia Creative Commons AtribuciónNoComercial-CompartirIgual 4.0 Internacional.

# Índice general

| Agra         | adecimientos                                                    | 8  |

|--------------|-----------------------------------------------------------------|----|

| Res          | umen                                                            | 9  |

| Nomenclatura |                                                                 | 10 |

| 1.           | Introducción                                                    | 12 |

|              | 1.1. Comunicaciones por la red eléctrica (PLC)                  | 12 |

|              | 1.1.1. Tipos de PLC                                             | 13 |

|              | 1.2. Problemáticas asociadas a PLC                              | 13 |

|              | 1.2.1. Modelado del canal                                       | 14 |

|              | 1.2.2. Fuentes de ruido                                         | 14 |

|              | 1.3. Esquema básico de PLC                                      | 15 |

|              | 1.4. Sistema PLC de banda angosta                               | 16 |

|              | 1.4.1. Regulaciones regionales                                  | 16 |

|              | 1.4.2. Transmisión en banda angosta                             |    |

|              | 1.5. Objetivos                                                  | 22 |

| 2.           | Diseño del sistema                                              | 23 |

|              | 2.1. Método de medición                                         | 23 |

|              | 2.2. Generación de la señal de medición                         | 24 |

|              | 2.2.1. Señal de barrido (chirp)                                 | 24 |

|              | 2.2.2. Conversor digital-analógico (DAC)                        | 30 |

|              | 2.2.3. Amplificador de potencia                                 | 32 |

|              | 2.3. Acoplador de red                                           | 34 |

|              | 2.3.1. Filtro de salida                                         | 35 |

|              | 2.3.2. Transformador de acoplamiento                            | 35 |

|              | 2.3.3. Dispositivos de protección                               | 36 |

|              | 2.4. Medición y procesamiento de señales                        | 37 |

|              | 2.4.1. Cálculo de la impedancia de línea ( $Z_L$ )              | 38 |

|              | 2.4.2. Método de calibración                                    | 39 |

|              | 2.4.3. Amplificación y adquisición de señales ( $V_T$ e $I_T$ ) | 42 |

| 3.           | Implementación del sistema                                      | 47 |

|              | 3.1. Generación de chirp analógica                              | 48 |

|              | 3.1.1. Amplificador de potencia (OPA564)                        |    |

|              | 3.1.1.1. Ajuste del límite de corriente (I <sub>LIM</sub> )     | 48 |

|              | 3 1 1 2 Monitoreo de señales de control (Isua y Trus)           | Δ٧ |

| 3.1.1.3. Fuentes de alimentación, gar                   | nancia y amplitud de salida51                       |

|---------------------------------------------------------|-----------------------------------------------------|

| 3.1.1.4. Fuente de alimentación digita                  | al52                                                |

| 3.1.1.5. Compensación y protección o                    | de la etapa de salida53                             |

| 3.1.1.6. Disipación térmica                             | 54                                                  |

| 3.1.2. Conversor digital-analógico (DAC) y p            | re-amplificador56                                   |

| 3.2. Acoplador de red                                   | 57                                                  |

| 3.2.1. Filtro de salida                                 | 58                                                  |

| 3.2.2. Transformador de acoplamiento (T <sub>A</sub> ). | 58                                                  |

| 3.2.3. Dispositivos de protección (TVS y MO             | OV)60                                               |

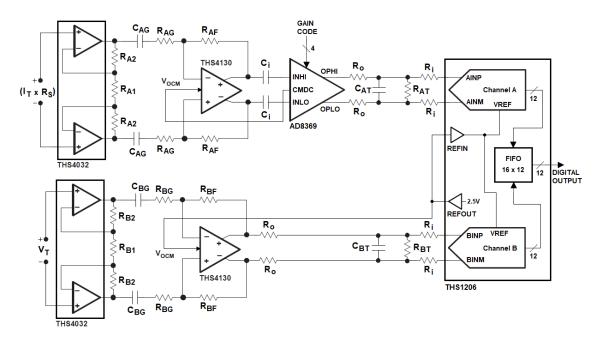

| 3.3. Amplificación y adquisición de señales ( $V_T$ e   | I <sub>T</sub> )61                                  |

| 3.3.1. Resistencia de medición de corriente             | (R <sub>S</sub> )62                                 |

| 3.3.2. Fuentes de alimentación y amplitud o             | de señales62                                        |

| 3.3.3. Ganancias de los amplificadores de in            | nstrumentación (G <sub>A</sub> y G <sub>B</sub> )64 |

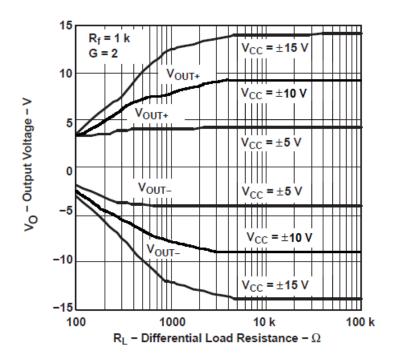

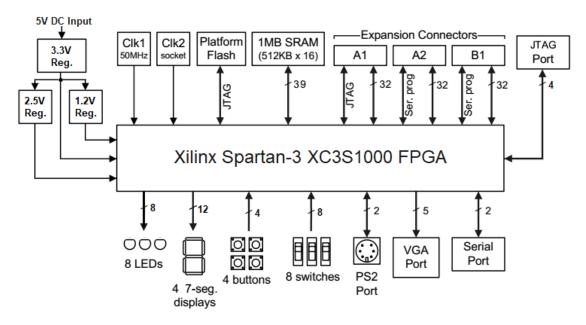

| 3.4. Control en lógica programable (FPGA)               | 66                                                  |

| 3.4.1. Recursos de hardware disponibles                 | 66                                                  |

| 3.4.2. Generación y adquisición digital de se           | eñales67                                            |

| 3.4.2.1. Frecuencias de muestreo y ca                   | antidad de muestras68                               |

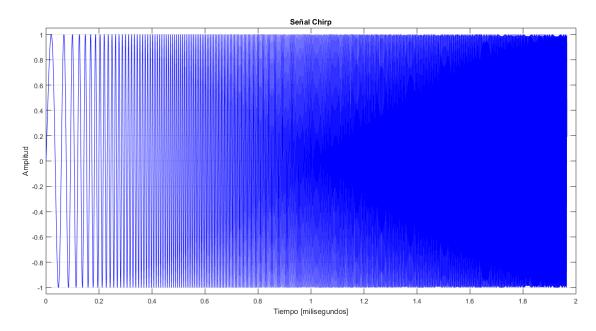

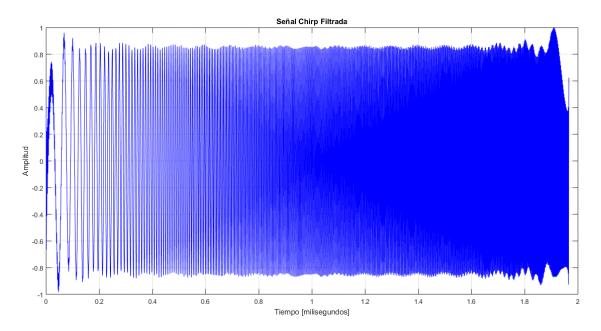

| 3.4.2.2. Generación de chirp digital                    | 69                                                  |

| 3.4.2.3. Proceso de medición y adqui:                   | sición de muestras72                                |

| 3.4.3. Requerimientos de hardware                       | 72                                                  |

| 3.4.3.1. Asignación de señales en con                   | nectores de expansión (A1 y A2)73                   |

| 3.4.4. Circuito lógico de control                       | 76                                                  |

| 3.4.4.1. Interfaz de comunicación ser                   | ie UART76                                           |

| 3.4.4.2. Interfaz de configuración y co                 | ontrol del ADC79                                    |

| 3.4.4.3. Memoria RAM                                    | 85                                                  |

| 3.4.4.4. Memoria ROM e Interfaz del                     | DAC87                                               |

| 3.4.4.5. Lógica de Control                              | 87                                                  |

| 3.5. Control en la PC (Python)                          | 89                                                  |

| 3.5.1. Procesamiento digital de señales                 | 89                                                  |

| 3.5.2. Monitoreo del amplificador de poten              | cia (OPA)90                                         |

| 3.5.3. Control automático de ganancia (AGC              | C)90                                                |

| 3.5.4. Integración de puertos por USB                   | 92                                                  |

| 3.5.4.1. Configuración del FT2232H M                    | /lini Module92                                      |

| 3.5.4.2. Programación de la FPGA (XC                    | C3SPROG)95                                          |

| 3.5.5. Programa de control e Interfaz de usu            | uario95                                             |

| 3.5.5.1. Módulos de extensión y mód                     | lulos de programa95                                 |

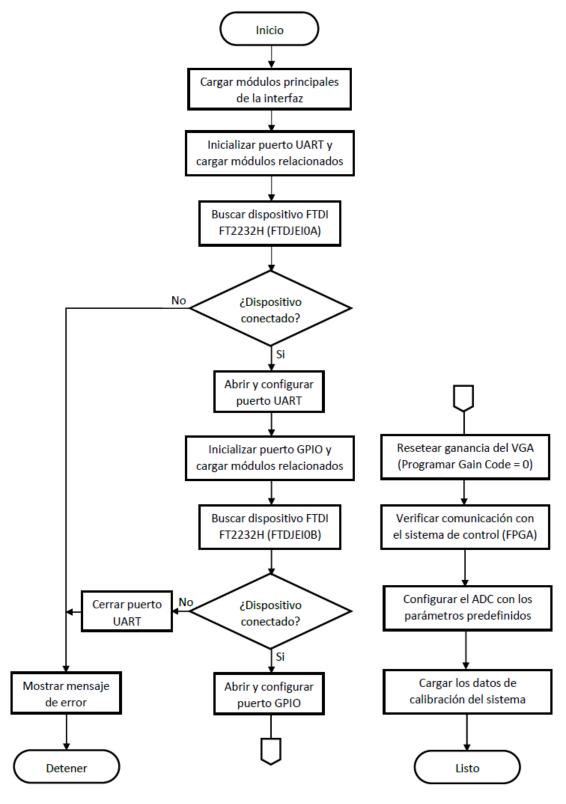

|     | 3.5.5.2. Inicialización de la interfaz de usuario              | 97  |

|-----|----------------------------------------------------------------|-----|

|     | 3.5.5.3. Funciones de chequeo, recuperación y cierre           | 99  |

|     | 3.5.5.4. Función de programación de ganancia                   | 99  |

|     | 3.5.5.5. Función de medición y ploteo de señales               | 99  |

|     | 3.5.5.6. Función de calibración del sistema                    | 100 |

|     | 3.5.5.7. Función de medición simple de impedancia              | 100 |

|     | 3.5.5.8. Función de ploteo simple de impedancia                | 101 |

|     | 3.5.5.9. Función de medición múltiple de impedancia            | 101 |

|     | 3.5.5.10. Función de ploteo múltiple de impedancia             | 102 |

|     | 3.6. Evaluación en entorno de simulación                       | 103 |

|     | 3.6.1. Simulación del método de calibración                    | 103 |

|     | 3.6.2. Simulación del método de medición                       | 105 |

| 4.  | Resultados experimentales                                      | 108 |

| 5.  | Conclusiones                                                   | 114 |

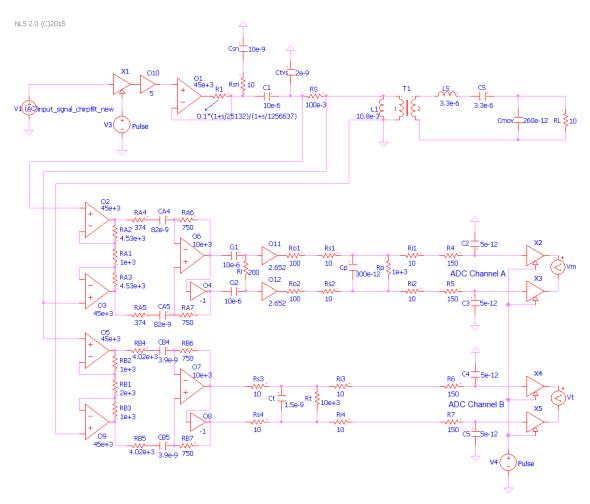

| A.  | Modelado y simulación del sistema                              | 115 |

|     | A.1. Modelos de simulación                                     | 116 |

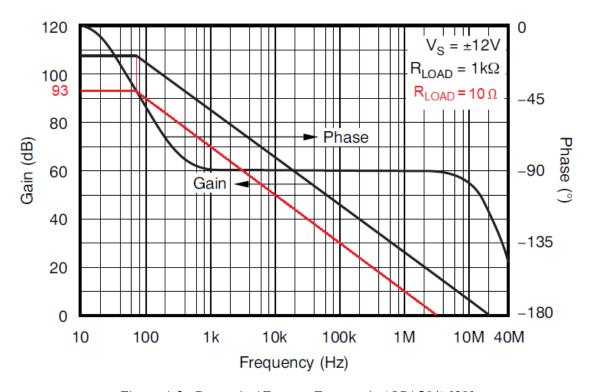

|     | A.1.1. Amplificadores operacionales (OPA564, THS4032, THS4130) | 116 |

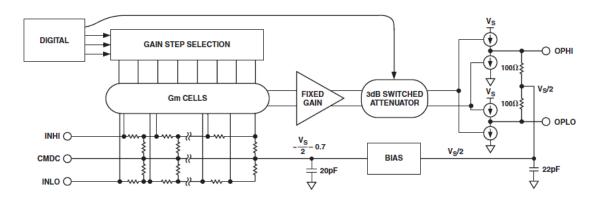

|     | A.1.2. Amplificador de ganancia variable (VGA)                 | 117 |

|     | A.1.3. Conversor analógico-digital (ADC)                       | 117 |

|     | A.1.4. Conversor digital-analógico (DAC)                       | 118 |

|     | A.1.5. Transformador de acoplamiento (T <sub>A</sub> )         | 119 |

|     | A.2. Respuesta en frecuencia (Bode)                            | 119 |

| В.  | Esquemáticos del circuito y PCB                                | 123 |

| Rih | lingrafía                                                      | 123 |

# Índice de figuras y tablas

| Figura 1.1: Diagrama en bloques básico de un sistema de comunicación PLC                                               | 15 |

|------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1.2: Bandas de frecuencia reguladas para PLC de banda angosta                                                   | 16 |

| Figura 1.3: Máximo nivel de salida para bandas reguladas por CENELEC EN 50065-1 [13]                                   | 17 |

| Figura 1.4: Esquema básico de transmisión de un sistema PLC de banda angosta                                           | 18 |

| Figura 1.5: Tensión de salida en función de la impedancia de línea para un modem PLC<br>TDA5051A [16]                  | 19 |

| Figura 1.6: Forma de onda del ruido presente en el punto de recepción [23]                                             | 20 |

| Figura 1.7: Forma de onda de la señal recibida para una transmisión en el mismo punto de recepción [23].               | 20 |

| Figura 1.8: Forma de onda de la señal recibida para una transmisión a una distancia aproximada de 20 metros [23]       | 21 |

| Figura 2.1: Diagrama en bloques del sistema.                                                                           | 23 |

| Figura 2.2: Forma de onda de una chirp lineal; onda senoidal que aumenta en frecuencia linealmente con el tiempo [33]. | 25 |

| Figura 2.3: Espectros de potencia de una chirp lineal [34].                                                            | 28 |

| Figura 2.4: Fase residual de una chirp lineal [34]                                                                     | 28 |

| Figura 2.5: Fracción de potencia de una chirp por fuera del rango de barrido [34]                                      | 29 |

| Figura 2.6: Esquema de conversión de señal digital a señal analógica                                                   | 31 |

| Figura 2.7: Amplificador OPA564 - (a) configuración de pines, (b) diagrama funcional                                   | 33 |

| Figura 2.8: Circuito simplificado de acoplador PLC capacitivo                                                          | 34 |

| Figura 2.9: Circuito de acoplamiento PLC                                                                               | 36 |

| Figura 2.10: Circuito de acoplador PLC con dispositivos de protección                                                  | 37 |

| Figura 2.11: Medición de señales en el circuito.                                                                       | 38 |

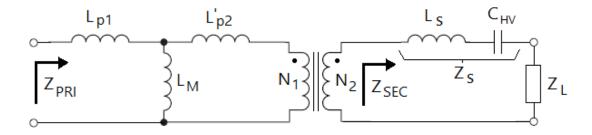

| Figura 2.12: Modelo no ideal del transformador de acoplamiento                                                         | 39 |

| Figura 2.13: Circuito simplificado del transformador de acoplamiento                                                   | 40 |

| Figura 2.14: Amplificador de instrumentación.                                                                          | 43 |

| Figura 2.15: Diagrama en bloques general del amplificador de ganancia variable                                         | 44 |

| Figura 2.16: Circuito de amplificación y adquisición de las señales $V_T$ e $I_T$                                      | 45 |

| Figura 3.1: Diagrama en bloques funcional del sistema.                                                                 | 47 |

| Figura 3.2: Circuito equivalente del amplificador OPA564 con la salida apagada [30]                                    | 50 |

| Figura 3.3: Circuito de monitoreo opto-acoplado de las señales digitales del OPA564                                    | 51 |

| Figura 3.4: Tensión de salida vs. Corriente de salida (OPA564) [30]                                                    | 51 |

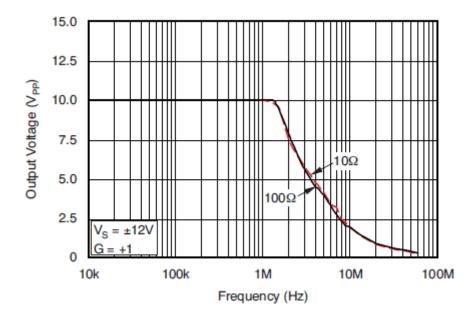

| Figura 3.5: Tensión de salida vs. Frecuencia de operación (OPA564) [30]                                                | 52 |

| Figura 3.6: Circuito para generar la tensión V <sub>DIG</sub> del OPA564                                               | 53 |

| Figura 3.7: Circuito de compensación y protección de la etapa de salida (OPA564) [30]      | 54   |

|--------------------------------------------------------------------------------------------|------|

| Figura 3.8: Circuito simplificado del amplificador de potencia                             | 55   |

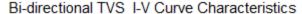

| Figura 3.9: Curva característica (corriente-tensión) de un TVS bidireccional [74]          | 61   |

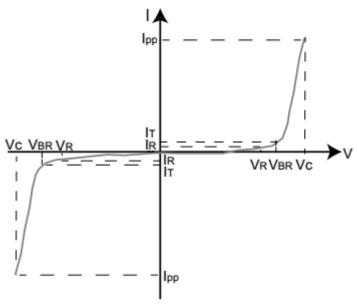

| Figura 3.10: Tensión de salida vs. Resistencia de carga diferencial (THS4130) [41]         | 63   |

| Figura 3.11: Digilent Spartan-3 Starter Kit Board                                          | 66   |

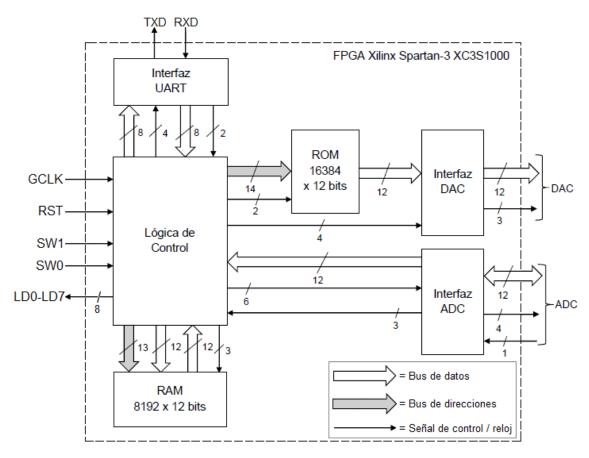

| Figura 3.12: Diagrama en bloques del kit de desarrollo en FPGA                             | 67   |

| Figura 3.13: Forma de onda de la señal chirp de tiempo discreto                            | 70   |

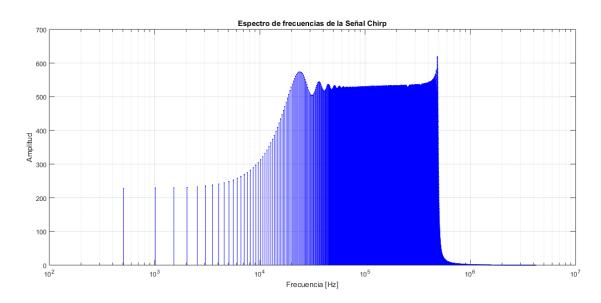

| Figura 3.14: Espectro de frecuencias discreto de la señal chirp                            | 70   |

| Figura 3.15: Forma de onda de la señal chirp filtrada                                      | 71   |

| Figura 3.16: Espectro de frecuencias discreto de la señal chirp filtrada                   | 71   |

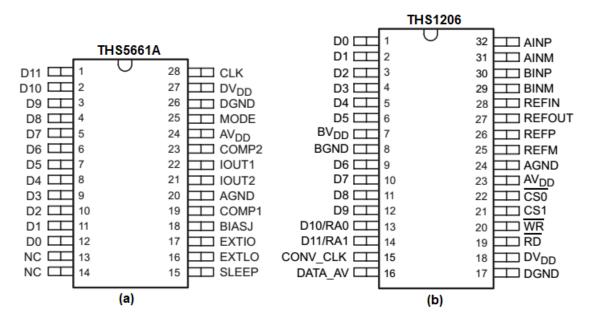

| Figura 3.17: Diagrama de asignación de pines – (a) DAC THS5661A, (b) ADC THS1206           | 73   |

| Tabla 3.1: Asignación de señales en el conector de expansión A1                            | 74   |

| Tabla 3.2: Asignación de señales en el conector de expansión A2                            | 75   |

| Figura 3.18: Diagrama en bloques del circuito lógico implementado en la FPGA               | 76   |

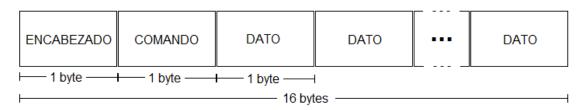

| Figura 3.19: Formato de paquete de datos utilizado para los comandos de control            | 77   |

| Tabla 3.3: Comandos de control del sistema                                                 | 78   |

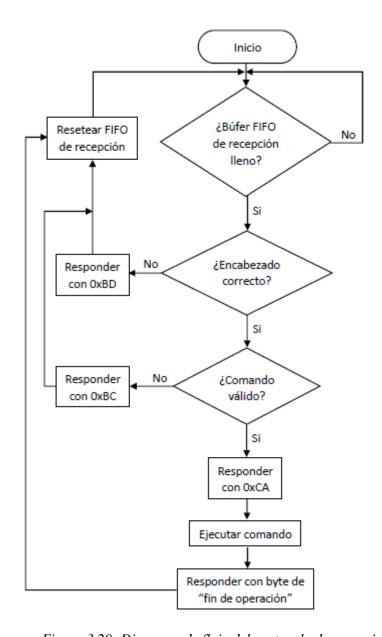

| Figura 3.20: Diagrama de flujo del protocolo de comunicación                               | 78   |

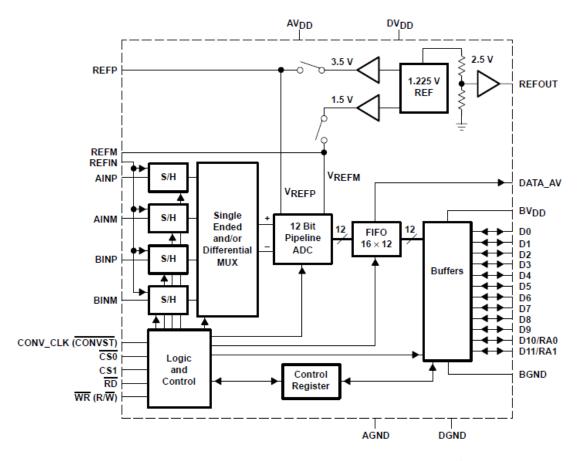

| Figura 3.21: Diagrama de bloques funcional del ADC THS1206 [43].                           | 79   |

| Tabla 3.4: Valores de bits programados en el registro CRO del ADC THS1206                  | 80   |

| Tabla 3.5: Valores de bits programados en el registro CR1 del ADC THS1206                  | 80   |

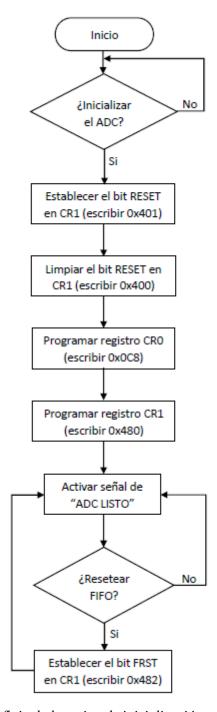

| Figura 3.22: Diagrama de flujo de la rutina de inicialización y configuración del ADC      | 82   |

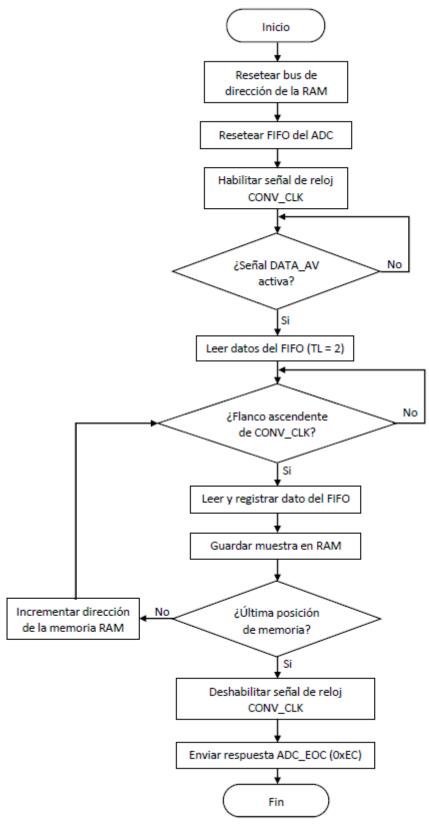

| Figura 3.23: Diagrama de flujo del proceso de conversión y lectura de muestras del ADC     | 84   |

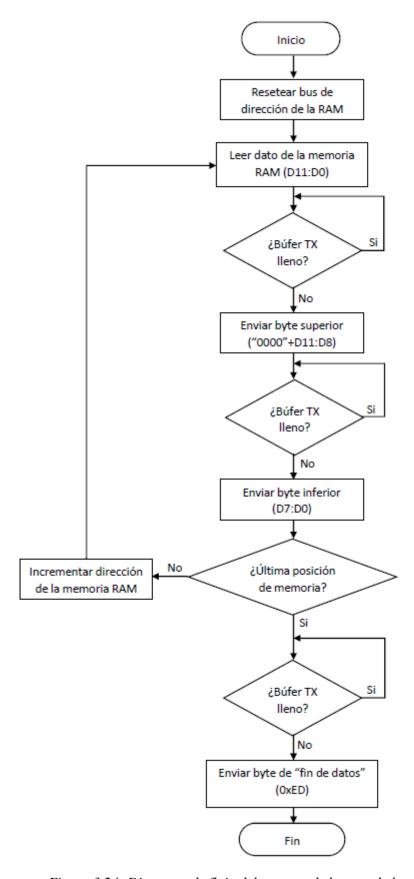

| Figura 3.24: Diagrama de flujo del proceso de lectura de la memoria RAM                    | 86   |

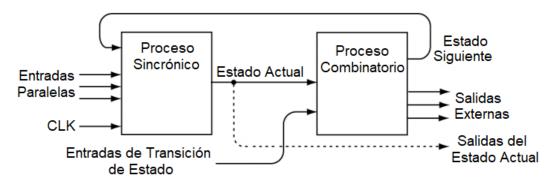

| Figura 3.25: Diagrama del modelo de implementación en VHDL de la FSM                       | 88   |

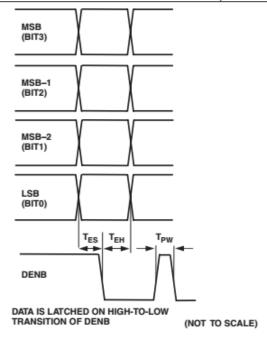

| Figura 3.26: Programación del código de ganancia con interfaz paralela [42]                | 91   |

| Figura 3.27: FTDI USB Hi-Speed FT2232H Mini Module [54].                                   | 93   |

| Tabla 3.6: Asignación de señales en el conector CN2 (FT2232H Mini Module)                  | 94   |

| Tabla 3.7: Asignación de señales en el conector CN3 (FT2232H Mini Module)                  | 94   |

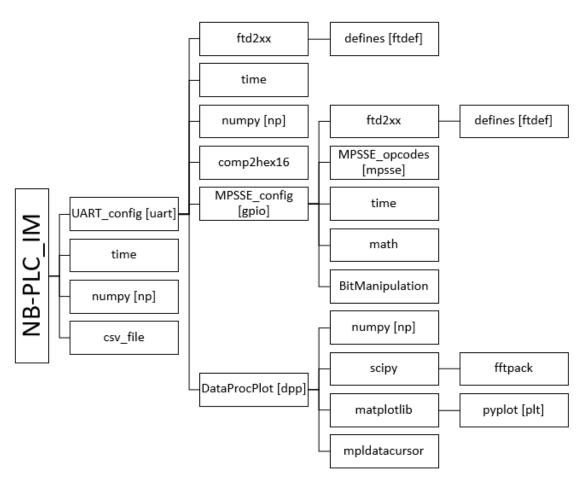

| Figura 3.28: Diagrama de jerarquía multinivel de la estructura del programa                | 97   |

| Figura 3.29: Diagrama de flujo de la rutina de inicialización de la interfaz de usuario    | 98   |

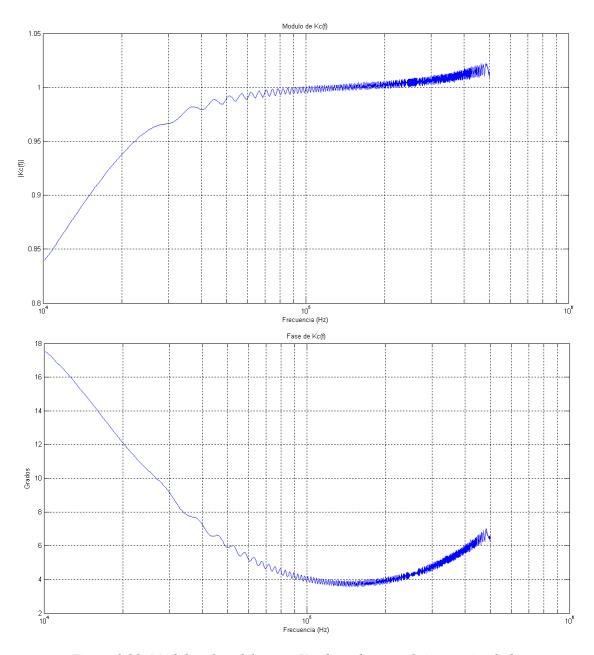

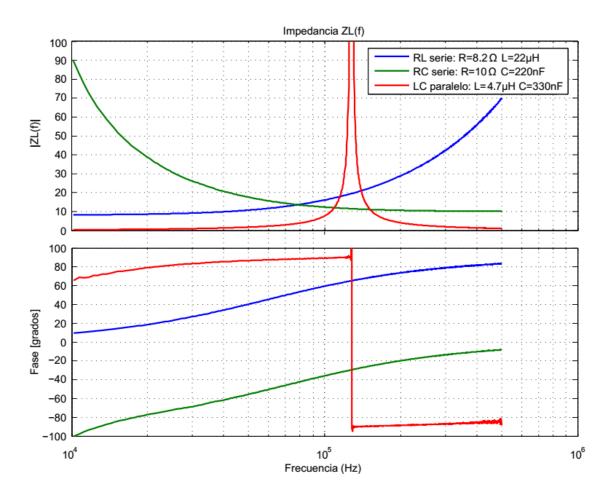

| Figura 3.30: Módulo y fase del vector $K_C$ obtenido para el sistema simulado              | 104  |

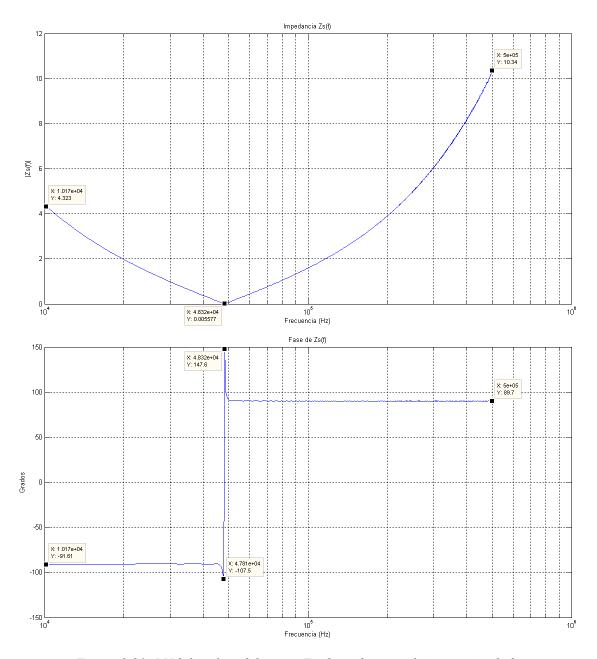

| Figura 3.31: Módulo y fase del vector $Z_S$ obtenido para el sistema simulado              | 105  |

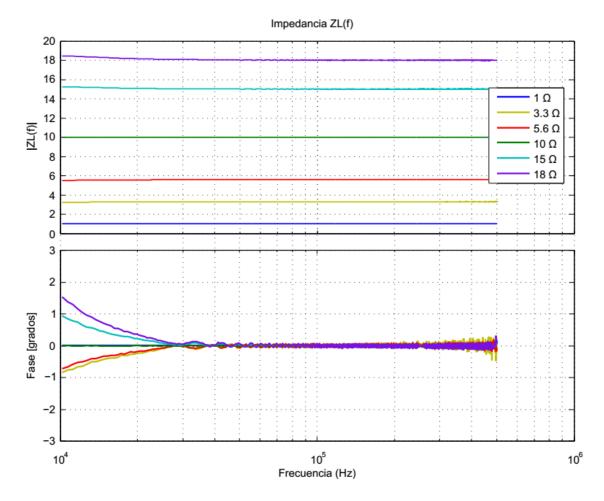

| Figura 3.32: Magnitud y fase de la impedancia para diferentes cargas resistivas            | 106  |

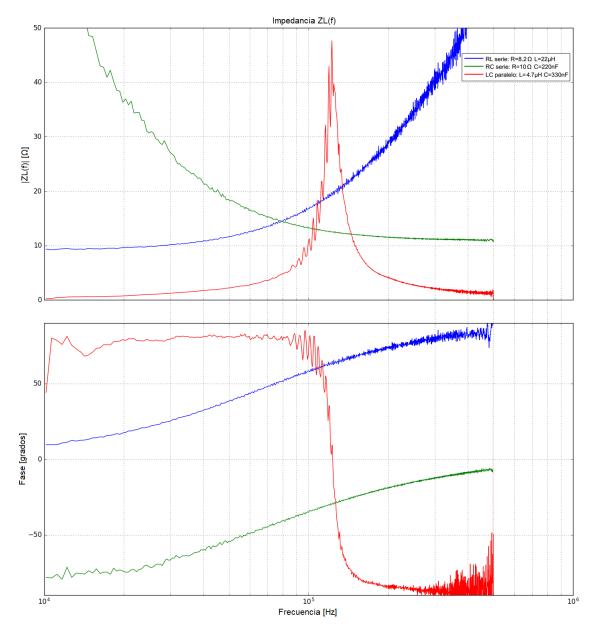

| Figura 3.33: Magnitud y fase de la impedancia para cargas complejas                        | 107  |

| Figura 4.1: Sistema PLC de banda angosta para la caracterización de la impedancia de la re | ed . |

| eléctrica                                                                                  | 108  |

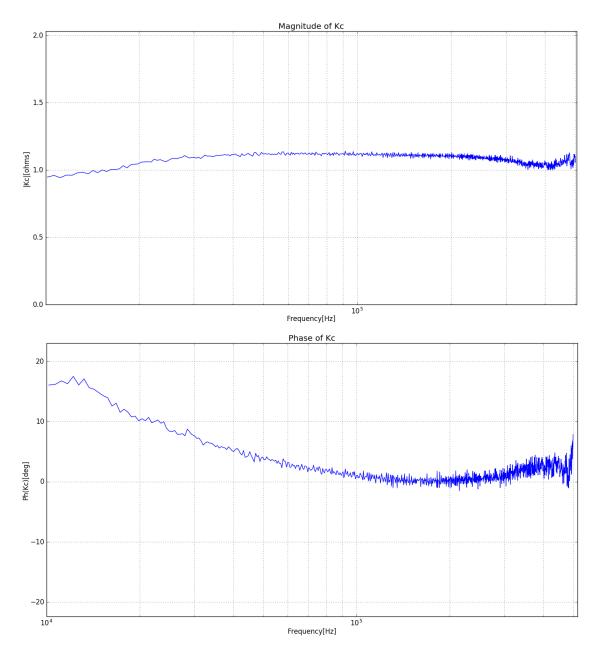

| Figura 4.2: Magnitud y fase del vector K <sub>c</sub>                                     | 109 |

|-------------------------------------------------------------------------------------------|-----|

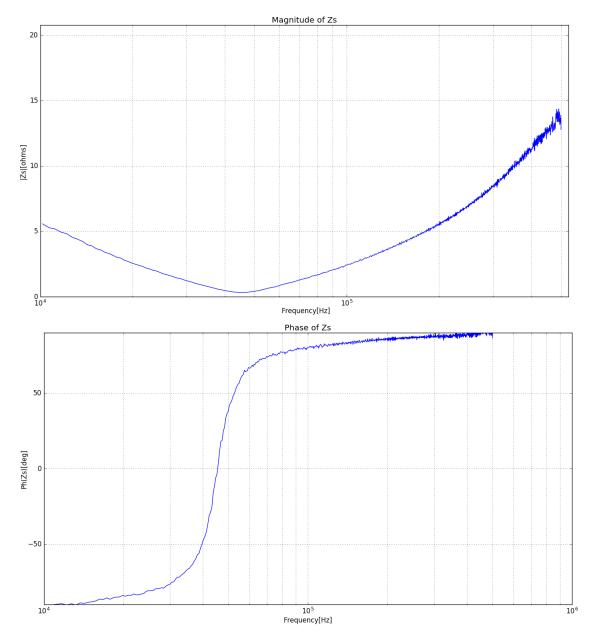

| Figura 4.3: Magnitud y fase del vector Z <sub>s</sub> .                                   | 110 |

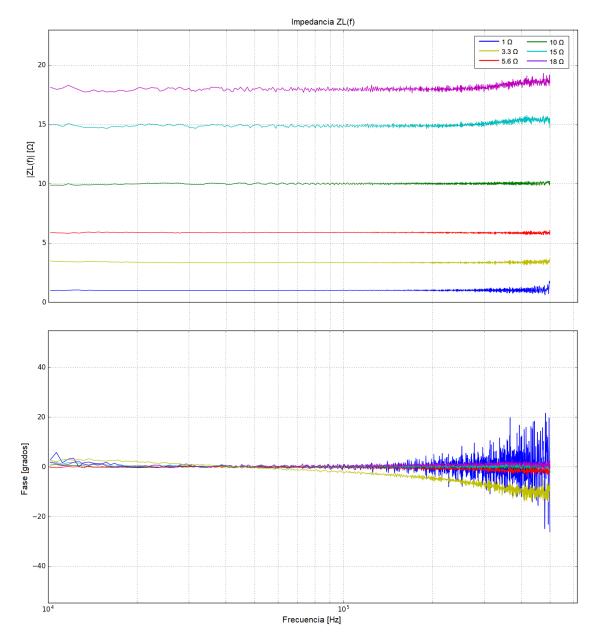

| Figura 4.4: Magnitud y fase de la impedancia $Z_L$ para diferentes cargas resistivas      | 111 |

| Figura 4.5: Magnitud y fase de la impedancia $Z_L$ para cargas complejas                  | 112 |

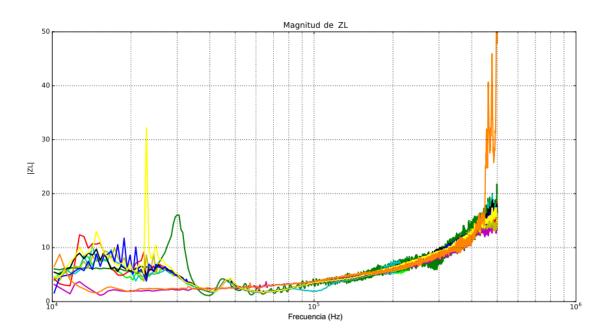

| Figura 4.6: Magnitud de la impedancia de línea para un total de diez mediciones           | 113 |

| Figura A.1: Esquemático del circuito simulado en el programa NL5                          | 115 |

| Figura A.2: Ganancia / Fase vs. Frecuencia (OPA564) [30].                                 | 116 |

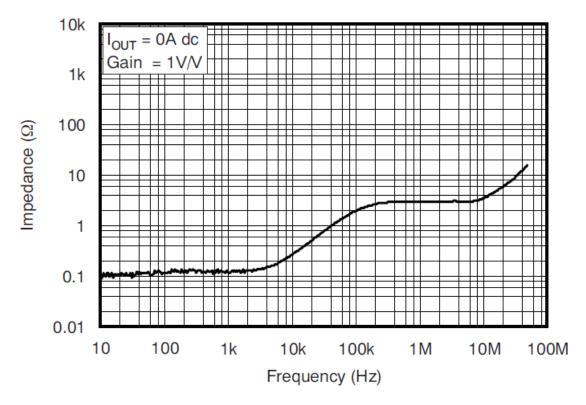

| Figura A.3: Impedancia de salida a lazo cerrado sin carga (OPA564) [30]                   | 117 |

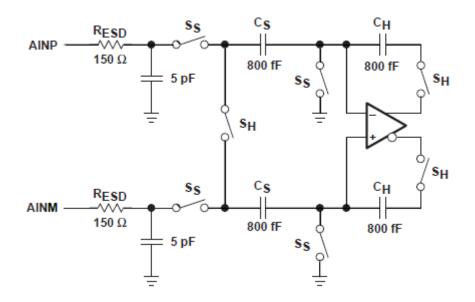

| Figura A.4: Esquema de entrada analógica equivalente del ADC (THS1206) [61]               | 118 |

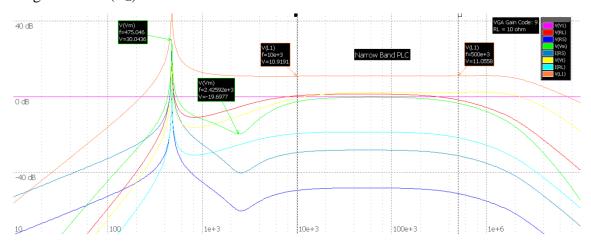

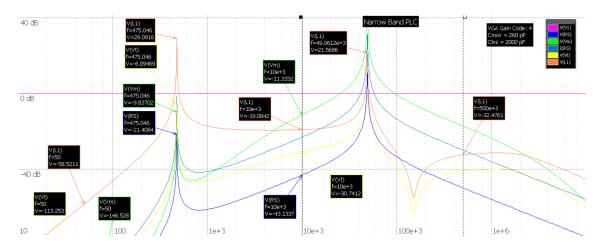

| Figura A.5: Respuesta en frecuencia del circuito simulado ( $R_L$ =10 $\Omega$ )          | 119 |

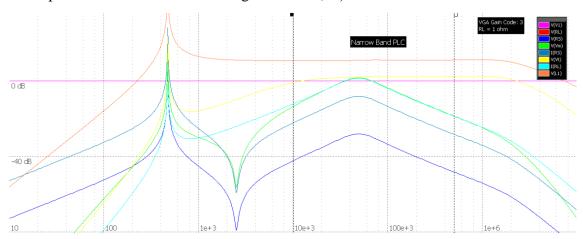

| Figura A.6: Respuesta en frecuencia del circuito simulado ( $R_L$ =1 $\Omega$ )           | 120 |

| Figura A.7: Respuesta en frecuencia del circuito para señal inyectada en la salida        | 122 |

| Tabla B.1: Listado de los componentes del circuito.                                       | 124 |

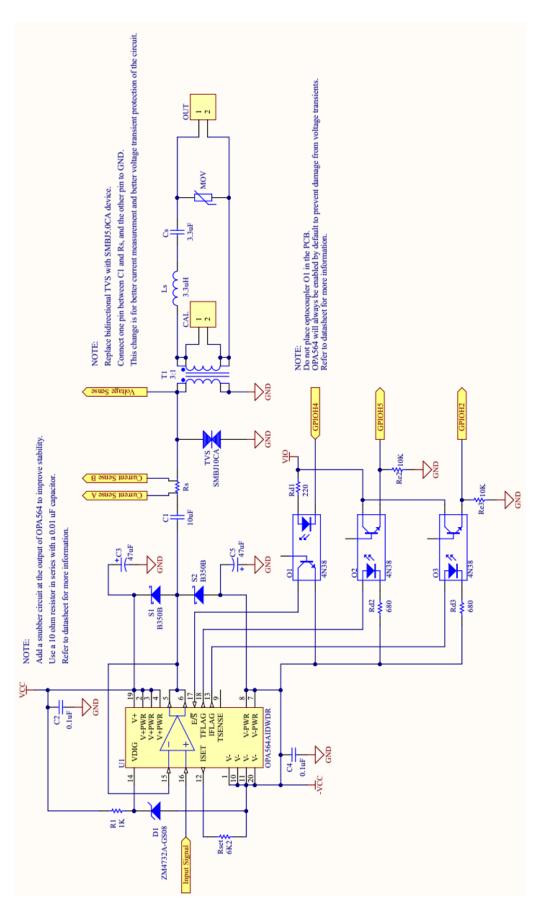

| Figura B.1: Esquemático de la etapa de potencia (OPA) y el acoplador de red               | 127 |

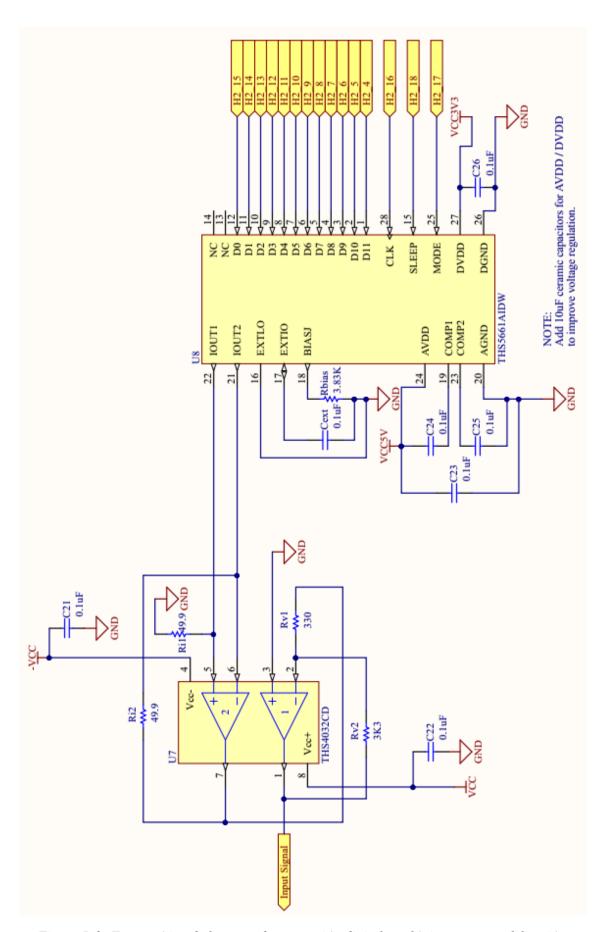

| Figura B.2: Esquemático de la etapa de conversión digital-analógica y pre-amplificación   | 128 |

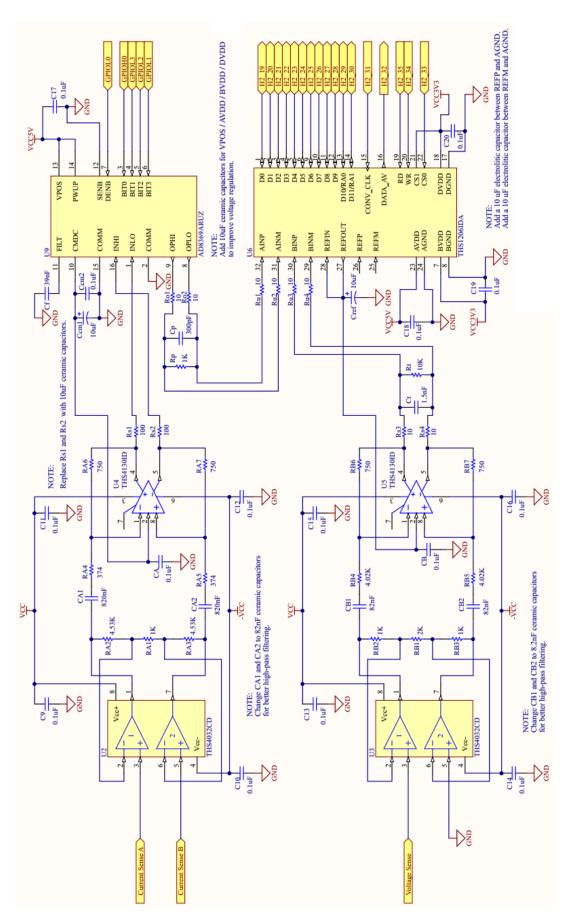

| Figura B.3: Esquemático de la etapa de adquisición de señales y conversión analógica-digi |     |

|                                                                                           | 129 |

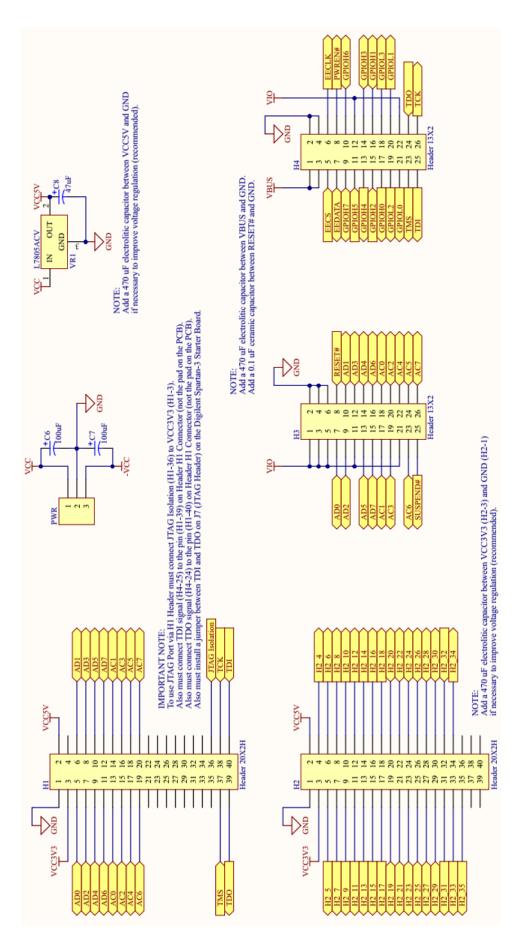

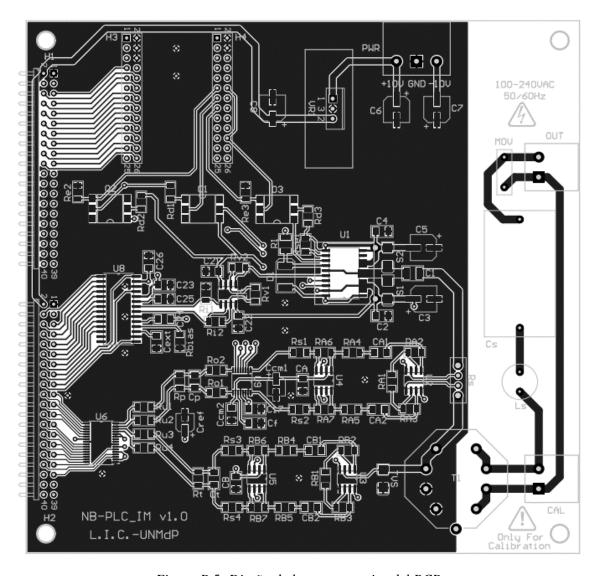

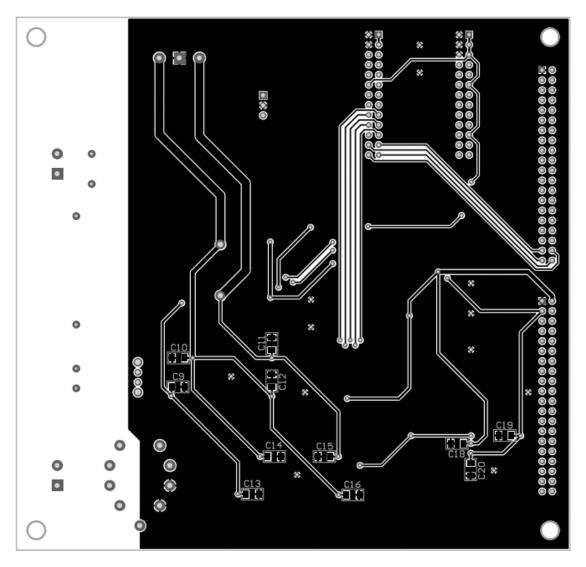

| Figura B.4: Esquemático de los conectores de expansión y las fuentes de alimentación      | 130 |

| Figura B.5: Diseño de la capa superior del PCB.                                           | 131 |

| Figura B.6: Diseño de la capa inferior del PCB.                                           | 132 |

# Agradecimientos

A mis directores Matías Hadad y Marcos Funes por la orientación y ayuda que me brindaron durante el desarrollo del trabajo que concluyó en esta tesis.

A mis colegas del Laboratorio de Instrumentación y Control por su compañerismo y solidaridad.

# Resumen

Este trabajo discute el diseño e implementación de un sistema para la caracterización de la impedancia de la red de baja tensión para las comunicaciones por la red eléctrica (PLC) en banda angosta. El diseño del sistema involucra el desarrollo de una etapa de potencia y acoplamiento a la red eléctrica junto con el circuito de adquisición de las señales requeridas para su procesamiento digital y el posterior cálculo de la impedancia.

El hardware de control digital del sistema se implementa en lógica programable sobre una placa de desarrollo en FPGA, utilizando lenguaje VHDL para su diseño. Además, la interfaz de control del sistema para la configuración, calibración, medición y presentación de resultados, se implementa por medio de un programa de PC desarrollado en lenguaje Python.

# Nomenclatura

ADC Conversor analógico-digital

(Analog-to-Digital Converter)

AGC Control automático de ganancia

(Automatic Gain Control)

AC Corriente alterna

(Alternating Current)

BPL Banda ancha sobre líneas eléctricas

(Broadband over Power Lines)

CMOS Semiconductor complementario de óxido metálico

(Complementary Metal Oxide Semiconductor)

CSV Valores separados por comas

(Comma-separated Values)

DAC Conversor digital-analógico

(Digital-to-Analog Converter)

FIFO Primero en entrar, primero en salir

(First In, First Out)

FFT Transformada rápida de Fourier

(Fast Fourier Transform)

FPGA Matriz de compuertas lógicas programables

(Field-programmable Gate Array)

FSM Máquina de estados finitos

(Finite State Machine)

FSK Modulación por desplazamiento de frecuencia

(Frequency Shift Keying)

GPIO Entrada/salida de propósito general

(General Purpose Input/Output)

GUI Interfaz gráfica de usuario

(Graphics User Interface)

IDLE Entorno de desarrollo integrado

(Integrated DeveLopment Environment)

LSB Bit menos significativo

(Least Significant Bit)

MOV Varistor de óxido metálico

(Metal Oxide Varistor)

MSB Bit más significativo

(Most Significant Bit)

MSPS Millones de muestras por segundo

(Million Samples Per Second)

NB-PLC PLC de banda angosta

(Narrow-band PLC)

OOK Modulación por encendido-apagado

(On-Off Keying)

PCB Placa de circuito impreso

(Printed Circuit Board)

PLC Comunicaciones por la red eléctrica

(Power Line Communicactions)

PSK Modulación por desplazamiento de fase

(Phase Shift Keying)

RAM Memoria de acceso aleatorio

(Random-access Memory)

ROM Memoria de sólo lectura

(Read-only Memory)

TL Nivel de disparo o activación

(Trigger Level)

TVS Diodo de supresión de transitorios de tensión

(Transient Voltage Supression)

UART Transmisor-receptor asíncrono universal

(Universal Asynchronous Receiver-Transmitter)

VGA Amplificador de ganancia variable

(Variable Gain Amplifier)

VHDL Lenguaje de descripción de hardware VHSIC

(VHSIC Hardware Description Language)

V<sub>PP</sub> Tensión pico a pico

(Peak-to-peak Voltage)

# 1. Introducción

Existe un interés creciente por las aplicaciones de los sistemas de comunicaciones por la red eléctrica, especialmente impulsado por nuevos conceptos tecnológicos, tales como las redes eléctricas inteligentes (*Smart grids*). En el marco de este nuevo concepto de redes eléctricas, existe la necesidad de mejorar los sistemas de comunicación para las aplicaciones de medición o de control entre subestaciones y usuarios.

La comunicación de datos sobre la red eléctrica presenta algunas problemáticas, entre las que se encuentran, una presencia de ruido que dista de ser el comúnmente conocido ruido blanco aditivo gaussiano (AWGN), y una impedancia que varía con el tiempo y la posición. Esta última es especialmente perjudicial debido a que en ocasiones es inferior a la contemplada por normas y equipos comerciales por lo que produce una gran atenuación de las señales inyectadas a la red. Como consecuencia, la señal inyectada se ve deteriorada aún más por el ruido presente ocasionando errores en la comunicación o directamente una pérdida de alcance de la misma.

# 1.1. Comunicaciones por la red eléctrica (PLC)

El tendido de energía eléctrica conforma la red física más extensa del mundo. Está formada por miles de kilómetros de cable y llega a más de 3000 millones de personas, ofreciendo servicios incluso en aquellos lugares donde no hay acceso a otras redes cableadas. De esta manera, la alta capilaridad de la red de distribución de energía eléctrica, entendiendo capilaridad como la capacidad que tiene una red para ramificarse progresivamente hasta alcanzar el usuario final, asegura el acceso al servicio en zonas donde otras redes, como la de telefonía, no llegan. Utilizar esta extensa red para la transmisión de datos es una realidad tangible por medio de la tecnología de comunicaciones por la red eléctrica, también conocida por la sigla PLC (Power Line Communications).

La transmisión de datos por la red eléctrica es un concepto que surgió en las primeras décadas del siglo XX, cuando se propuso su utilización para telefonía [1][2]. Esta tecnología ha sido estudiada desde los años 50, con fines de control remoto de recursos. En 1950 se desarrolló el primer sistema PLC, conocido como Ripple Control, para aplicaciones en redes eléctricas de baja y media tensión. Este sistema trabajaba en forma unidireccional y empleaba una frecuencia de portadora entre 100 Hz y 1 kHz. En 1960 la empresa de electricidad de Francia, EDF, puso en marcha el primer sistema industrial, denominado Pulsadis [3], mediante el cual se enviaban ráfagas codificadas de una señal de 175 Hz. Dicha señal era empleada para comandar equipos a distancia, como por ejemplo el alumbrado público, o para encender equipos en horarios determinados (por ejemplo, horarios de bajo consumo, donde la tarifa es más económica). En años posteriores, las empresas de energía eléctrica comenzaron a utilizar sus tendidos eléctricos internamente para la transmisión

de información a baja velocidad entre subestaciones, implementando sistemas PLC en líneas de media y alta tensión.

Hoy en día existen diversos servicios disponibles que utilizan esta tecnología en diferentes partes del mundo, principalmente en EEUU, Europa y Japón, y continúan los esfuerzos de investigación y desarrollo para la aplicación de estos sistemas en líneas de baja tensión.

#### 1.1.1. Tipos de PLC

Las comunicaciones por la red eléctrica pueden clasificarse generalmente como PLC de banda angosta (*narrowband PLC o NB-PLC*) para frecuencias menores a 500 kHz y PLC de banda ancha (*broadband PLC o BPL*) para frecuencias mayores (típicamente entre 2 MHz y 30 MHz), cada una con requerimientos y aplicaciones diferentes [7]. Además, la reglamentación para la transmisión en estas bandas es distinta y están reguladas por diferentes normas. Para PLC de banda angosta corresponde la normativa IEEE 1901.2 [10], mientras que PLC de banda ancha está regulado por el estándar IEEE 1901-2010 [11], que a su vez está basado en el sistema comercial orientado a Ethernet sobre el cableado eléctrico Homeplug AV [12].

A nivel general, se pueden distinguir funcionalmente cuatro aplicaciones básicas de PLC:

- Aplicaciones de banda angosta de uso interno, donde el cableado doméstico se utiliza para servicios de baja velocidad como automatización del hogar e intercomunicadores.

- Aplicaciones de banda angosta de uso externo, utilizadas por las empresas de servicios públicos para lectura automática de medidores, vigilancia y control remoto de sistemas varios.

- Aplicaciones de banda ancha de uso interno, donde el cableado de la red eléctrica se puede utilizar para la transmisión de datos a alta velocidad para redes domésticas.

- Aplicaciones de banda ancha de uso externo, donde el cableado de la red de alimentación eléctrica puede utilizarse para ofrecer acceso a Internet u otro servicio de banda ancha de datos.

## 1.2. Problemáticas asociadas a PLC

Es evidente que las redes eléctricas han sido diseñadas para distribuir energía y no para transmitir señales de comunicación. En particular, el uso de las líneas eléctricas internas de los edificios como medio de transmisión ha sido tradicionalmente desestimado por considerarse ruidoso y de características imprevisibles.

Sin embargo, el desarrollo de nuevas tecnologías y métodos de procesamiento de la información ha favorecido la utilización de este medio para la transmisión de datos. Aun así, el diseño e implementación de este tipo de sistemas no resulta una tarea sencilla

debido a las dificultades para caracterizar el canal como medio de transmisión y las perturbaciones asociadas.

#### 1.2.1. Modelado del canal

En general, el modelo de comportamiento de un canal suele estar descripto por una relación entrada-salida que representa su efecto sobre las señales, y un conjunto de perturbaciones caracterizadas estadísticamente que se añaden a la salida. Lograr este modelo de referencia para emplear en PLC no es una tarea sencilla puesto que las redes eléctricas presentan una gran diversidad entre distintos países, e incluso entre diferentes regiones y áreas de población. La intrincada topología de la red, muy ramificada, con líneas no terminadas y con cargas desadaptadas puede ser incluso desconocida, pues no suele haber planos del trazado y éste suele sufrir múltiples manipulaciones tras su instalación.

Por otro lado, la presencia de dispositivos presenta una carga heterogénea y variable en el tiempo que agrava las condiciones del canal, según se genera la conexión y desconexión de los aparatos eléctricos. Esto dificulta la caracterización de la red, aunque se pueden resumir algunas de sus consecuencias:

- La impedancia de la línea no es constante.

- La respuesta en frecuencia del sistema varía con el tiempo y la posición.

- La presencia de interferencia multi-camino variante en el tiempo.

- La generación de ondas reflejadas por desadaptación de impedancias.

Si bien aún no prevalece un modelo aceptado como estándar, existen trabajos de investigación dedicados implícitamente a su caracterización que han presentado algunas alternativas dentro de determinadas regiones [4][5], y que permiten modelar al canal como uno lineal y variante en el tiempo en forma periódica (LPTV, Linear periodic time variant). Además, existen algunas otras iniciativas, como el consorcio OPERA (Open PLC European Research Alliance) [6] que han aunado esfuerzos en investigación de sistemas PLC en Europa, produciendo algunos modelos de caracterización de la red.

#### 1.2.2. Fuentes de ruido

Una de las características más particulares del canal PLC es la fuerte presencia de ruido variante en el tiempo, no blanco, y muchas veces no Gaussiano. Esto es producto de la suma de formas de onda de diferentes dispositivos conectados a la red eléctrica.

El ruido del canal PLC se puede dividir en [7][8][9]:

- Ruido continuo invariante en el tiempo, que posee una envolvente constante por largos períodos de tiempo (al menos algunos ciclos de la frecuencia de red). Este ruido también es conocido como Ruido de fondo y puede incluir el ruido térmico causado por los amplificadores del receptor.

- Ruido continuo variante en el tiempo, que posee una envolvente que cambia sincrónicamente con la tensión de red, por lo que su período es de la mitad del

período de línea. Una fuente típica de este tipo de ruido son los aparatos eléctricos cuya fuente de alimentación es una tensión rectificada pero no filtrada. Otra causa de este tipo de ruido es la modificación de las características del canal a lo largo del ciclo de red.

- Ruido impulsivo cíclico sincrónico con la red, que es una clase de ruido compuesto por un tren de impulsos con una frecuencia igual o múltiplo de la frecuencia de red. Una causa típica de este tipo de ruido son los rectificadores controlados o los dimmers basados en tiristores. Estos dispositivos controlan la intensidad lumínica conmutando la corriente de línea en forma sincrónica, por lo que el ruido de conmutación también es sincrónico a la red. Un aparato con un motor con escobillas es otra fuente de este tipo de ruido. En este caso, la conmutación en las escobillas del motor es más frecuente, y debido a que la amplitud del ruido depende de la tensión de red, los impulsos tienen el mismo período que la red.

- Ruido impulsivo cíclico asincrónico con la red, que es un tipo de ruido compuesto

por un tren de impulsos con una frecuencia mucho mayor a la de red. Una causa

típica de esta clase de ruido son los reguladores conmutados.

- Ruido impulsivo esporádico, que está compuesto por impulsos que ocurren en momentos aleatorios, muy a menudo en períodos del orden de los segundos. Este ruido es causado por termostatos o cuando se acciona un interruptor.

- Ruido de banda angosta, que es causado por el acoplamiento de ondas de radio en los cables de la red eléctrica. La envolvente de este tipo de ruido copia de una manera casi exacta a las señales transmitidas por el aire.

# 1.3. Esquema básico de PLC

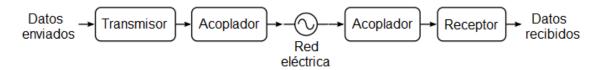

Como en todo sistema de comunicaciones, existe un esquema básico para la transmisión y recepción de un conjunto de datos a través de un canal determinado, como se muestra en la Figura 1.1.

Figura 1.1: Diagrama en bloques básico de un sistema de comunicación PLC.

Para que la comunicación sea posible, debe existir un sistema de transmisión que sea capaz de inyectar una señal determinada a la red, y otro que pueda extraerla y procesarla para recuperar los datos enviados. La interfaz con la red eléctrica se hace por medio de un circuito de acoplamiento capacitivo o inductivo, que también proporciona aislamiento galvánico y protección contra las perturbaciones de la tensión de línea. Además, como esta señal debe coexistir tanto con la tensión de línea de 50 o 60 Hz como con los distintos tipos de distorsión, la transmisión en banda base resulta imposible. Por lo tanto, es

necesario implementar algún tipo de modulación que permita utilizar la red eléctrica como canal.

Existe gran variedad de esquemas de modulación, cada uno con sus ventajas y desventajas. En particular, en el canal PLC, la aplicación de estos esquemas está ligada a la banda de frecuencia utilizada. En aplicaciones de PLC de banda angosta se suelen utilizar esquemas de modulación simples debido a su costo de implementación y simplicidad, mientras que en aplicaciones de PLC de banda ancha se utilizan técnicas de modulación más complejas, combinadas con esquemas de ecualización, como *Orthogonal Frequency Domain Multiplexing* (OFDM).

# 1.4. Sistema PLC de banda angosta

En aplicaciones de redes eléctricas inteligentes, la comunicación en banda angosta es de especial interés. Algunas de las aplicaciones más interesantes para este tipo de comunicación son la automatización en edificios y el hogar, gestión de recursos de energía renovable, control del alumbrado público y monitoreo de la red eléctrica por medio de medidores inteligentes. La implementación en cada uno de los casos tiene sus propios desafíos que dependen principalmente de las características variables del canal y los requerimientos asociados a las regulaciones existentes.

#### 1.4.1. Regulaciones regionales

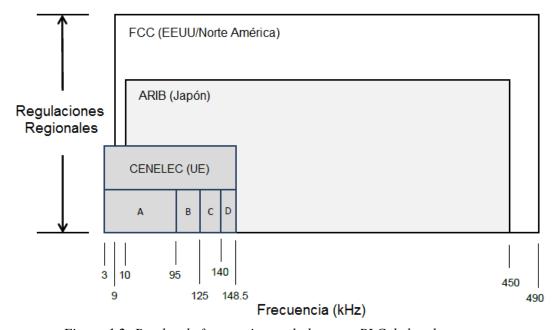

Como se mencionó anteriormente, la banda angosta de PLC ha sido enmarcada en el estándar IEEE 1901.2 [10], establecida para frecuencias menores a 500 kHz. Este estándar unifica las normas previamente establecidas y reguladas en diferentes países para esta banda PLC, como son: CENELEC EN 50065-1 [13], ARIB STD-T84 [14] y FCC Part 15 [15]. El diagrama de la Figura 1.2 resume la asignación de bandas de frecuencia según las regulaciones establecidas actualmente en diferentes regiones.

Figura 1.2: Bandas de frecuencia reguladas para PLC de banda angosta.

En este diagrama se puede observar que mientras que las normativas FCC de EEUU y ARIB de Japón proporcionan un mayor rango de frecuencias, el estándar Europeo CENELEC es más restrictivo, con la banda A de 3 kHz a 95 kHz reservada para aplicaciones de empresas de servicios públicos y sólo de 95 kHz a 148,5 kHz (bandas B, C y D) para aplicaciones de consumidores. Además, a diferencia de la normativa FCC que no impone límites en el nivel de señal inyectada, los niveles de señal máximos y emisiones electromagnéticas aceptadas por CENELEC son más estrictos (ver Figura 1.3).

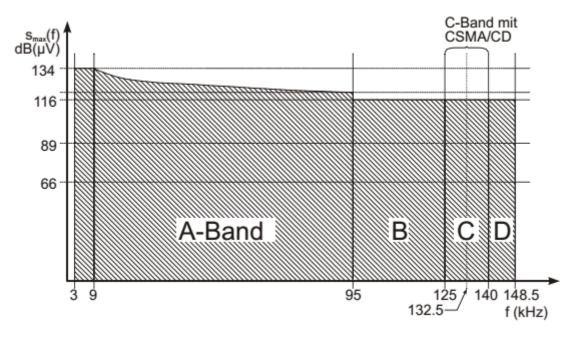

Figura 1.3: Máximo nivel de salida para bandas reguladas por CENELEC EN 50065-1 [13].

Para la transmisión a través de la red eléctrica, la normativa EN 50065-1 especifica que el máximo nivel de salida, dado en dB $\mu$ V, debe medirse con un *detector de nivel pico* y un circuito receptor determinado durante un período de un minuto. A su vez, define niveles de ruido para todas las bandas de frecuencia, obligatorios para cualquier artefacto eléctrico conectado a la red en Europa. De esta forma, la posible influencia parasitaria por las perturbaciones se reduce al mínimo.

#### 1.4.2. Transmisión en banda angosta

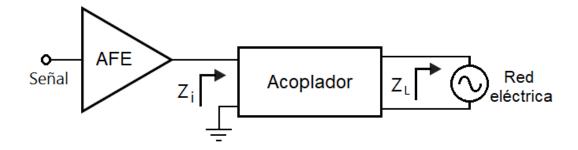

Cualquier sistema PLC debe implementar, para la transmisión de datos, una etapa analógica de salida junto a un circuito de acoplamiento, como se muestra en el esquema de la Figura 1.4. La etapa analógica (AFE o analog front-end, por sus siglas en inglés) de salida es la responsable de inyectar, a través del circuito de acoplamiento o acoplador, la señal modulada digitalmente a la red eléctrica y permitir así la transmisión de datos sobre la misma. Esta etapa está compuesta principalmente por un amplificador de potencia, que debe poseer una adecuada capacidad de corriente debido a la baja impedancia de línea que suele encontrarse en la red de baja de tensión para esta banda de frecuencias. Además de las funciones de acoplamiento, aislación galvánica y protección, el acoplador permite

hacer una adaptación de la impedancia de línea para que la impedancia vista por la etapa de salida sea la adecuada para su normal operación.

Figura 1.4: Esquema básico de transmisión de un sistema PLC de banda angosta.

Entre las alternativas presentes para PLC de banda angosta hay una diversa gama de circuitos integrados que permiten la implementación de sistemas de comunicación para aplicaciones particulares, como son: el TDA5051A de NXP [16], que utiliza una modulación OOK; el ST7580 de ST Microelectronics [17], que utiliza modulaciones FSK y PSK; el SM2200 de Semitech Semiconductors [18], que utiliza modulación OFDM; el AFE031 de Texas Instruments [19], que implementa solamente un front-end analógico, entre otros. La utilización de estos circuitos integrados ha demostrado un buen comportamiento para la comunicación por redes eléctricas en Europa y Estados Unidos [20][21][22], para las cuales se encuentran diseñados. Sin embargo, debido a las características de la red eléctrica local, la cual no se encuentra regulada por las normas de estas regiones, estos circuitos integrados no producen los resultados esperados, permitiendo sólo comunicaciones de baja velocidad con un alcance muy reducido. Las principales características que dificultan las comunicaciones en la red eléctrica local son los elevados niveles de ruido presente y la baja impedancia de línea, dos condiciones para las cuales los esquemas empleados en las soluciones comerciales no se encuentran preparados.

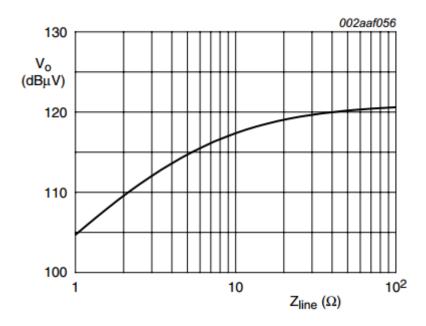

Un ejemplo del nivel de atenuación que puede sufrir la señal acoplada a la red cuando la impedancia de línea es baja se muestra en el gráfico de la Figura 1.5, que corresponde a la implementación típica de un modem PLC diseñado entorno al circuito integrado TDA5051A [16]. Se observa que el nivel de señal a la salida del amplificador de potencia se reduce considerablemente a medida que la impedancia de línea se hace menor a la considerada como típica para el diseño de ese circuito. Es importante aclarar que, en este caso, el nivel máximo de señal a la salida está limitado para cumplir con la normativa CENELEC EN50065-1.

Figura 1.5: Tensión de salida en función de la impedancia de línea para un modem PLC TDA5051A [16].

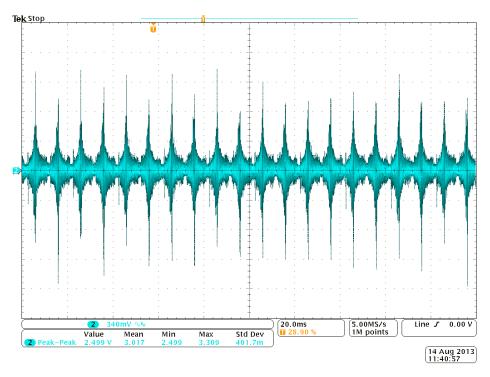

Otro ejemplo de la problemática que representa tener una baja impedancia de línea y altos niveles de ruido, se observó en ensayos de PLC en banda angosta que fueron realizados sobre la red eléctrica del Laboratorio de Instrumentación y Control de la Universidad Nacional de Mar del Plata, como parte del desarrollo de una tesis [23]. En estos ensayos se utilizaron dos prototipos de modem PLC que incorporan un front-end analógico basado en un AFE031 [19]. Las comunicaciones fueron realizadas en la banda CENELEC B con una frecuencia de portadora de 110 kHz y una amplitud igual a 1,25 V (~122 dBµV), utilizando un esquema de modulación PSK. En la Figura 1.6 se muestra el ruido presente en la red eléctrica en el punto de recepción de la comunicación, relevado a través del acoplador del modem PLC correspondiente. Se puede observar que el ruido es del tipo impulsivo cíclico sincrónico con la red y que posee una amplitud pico a pico relativamente grande, donde los impulsos se producen en los cruces por cero de la tensión de red.

Figura 1.6: Forma de onda del ruido presente en el punto de recepción [23].

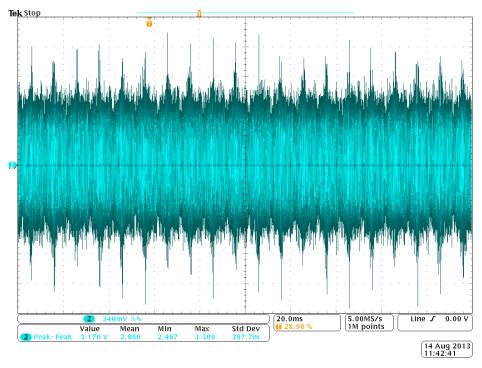

En la Figura 1.7 se muestra la señal recibida por el acoplador del correspondiente modem PLC cuando se realiza una transmisión sobre el mismo punto de recepción de la comunicación. Aquí se puede observar que la señal se ve afectada por los picos de ruido impulsivo y que tiene una amplitud estimada de 0,85 V por lo que se ha producido una atenuación ligeramente superior a los 3 dB en la señal inyectada como consecuencia de tener una baja impedancia de línea en el punto de transmisión.

Figura 1.7: Forma de onda de la señal recibida para una transmisión en el mismo punto de recepción [23].

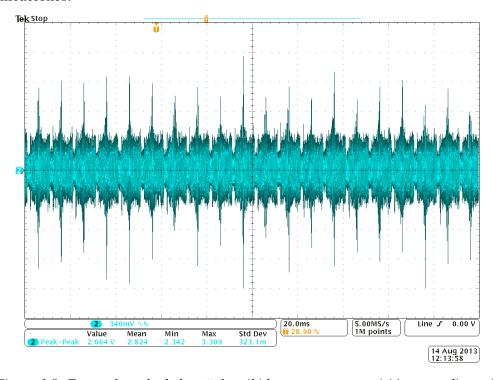

Por último, en la Figura 1.8 se muestra la señal recibida por el acoplador del modem PLC en el punto de recepción cuando se realiza una transmisión desde otro punto, con una longitud de cableado de la red de aproximadamente 20 metros. Se observa que la señal ha sufrido una importante atenuación al propagarse hasta el punto de recepción y además se advierte una mayor atenuación de esta señal en los puntos donde la tensión de red tiene los máximos. Como consecuencia, la demodulación directa de esta señal no permitió recuperar la información transmitida y fue necesario utilizar un esquema de codificación para lograr incrementar la relación señal a ruido. Este último caso evidencia la complejidad y variabilidad de las características de la red como canal de comunicaciones.

Figura 1.8: Forma de onda de la señal recibida para una transmisión a una distancia aproximada de 20 metros [23].

Como se puede notar, diseñar e implementar un sistema PLC de banda angosta no es una tarea sencilla pues implica conocer, aunque sea de forma aproximada, ciertas características de la red donde deberá operar ese sistema de comunicación. Una característica que es importante conocer es el valor de la impedancia de línea presente en los puntos donde de se va a inyectar la señal de comunicación. Hasta la fecha, se han llevado a cabo importantes investigaciones sobre la impedancia de la red eléctrica para aplicaciones PLC. Los experimentos anteriores pueden resumirse de la siguiente manera: Malack y Engstrom midieron 86 sistemas comerciales de distribución de energía AC de 50 Hz en seis países europeos y EE.UU. Estas mediciones muestran que la impedancia de las líneas eléctricas residenciales aumenta con la frecuencia y están en el rango de aproximadamente 1,5 a 80  $\Omega$  a una frecuencia de 100 kHz [24]. Vines *et al.* realizaron mediciones de impedancia de los circuitos residenciales de distribución de energía a frecuencias de 5 kHz a 20 kHz, e informaron que la impedancia de la línea de alimentación residencial es de 1 a 12  $\Omega$  [25]. Cavdar y Karadeniz realizaron mediciones

de impedancia de redes rurales, urbanas e industriales a frecuencias en el rango de 10 kHz a 170 kHz (Bandas CENELEC A, B, C, D) y obtuvieron valores en el rango de  $1 \text{ a } 21 \text{ }\Omega$  [26]. En conclusión se evidencia que, al menos para el rango de frecuencias bajas y medias de la banda angosta, la impedancia de la red eléctrica de baja tensión presenta valores tan bajos como  $1 \text{ }\Omega$  y un rango de variación de un orden de magnitud.

# 1.5. Objetivos

Teniendo en cuenta los aspectos descriptos, se propone diseñar, implementar y evaluar un sistema de caracterización de la impedancia de la red eléctrica de baja tensión para PLC de banda angosta en el rango comprendido entre 10 kHz y 500 kHz. Considerando que las aplicaciones de PLC en banda angosta sobre la red eléctrica local no se encuentran reguladas por una norma en particular, el rango de caracterización elegido abarcará a todas las bandas que si se encuentran reguladas en otras regiones. El objetivo principal de caracterizar la impedancia de la red eléctrica local es obtener valores de referencia, dentro de la banda de interés, para poder dimensionar correctamente las etapas de salida y acoplamiento de los sistemas de comunicación que operen en este entorno.

En cuanto a los objetivos particulares para el desarrollo del sistema propuesto, se pueden resumir en los siguientes:

- Desarrollo de la etapa de potencia y el circuito de acoplamiento a la red eléctrica.

- Aplicación de técnicas de medición y procesamiento de señales para la caracterización de la impedancia de la red eléctrica en la banda de interés.

- Desarrollo de la etapa de adquisición de las señales requeridas para su posterior procesamiento.

- Desarrollo de un programa de control del sistema basado en lógica programable.

- Desarrollo de una interfaz con la PC que permita la configuración, calibración, medición y presentación de resultados.

# 2. Diseño del sistema

En este capítulo se describe el método empleado para caracterizar la impedancia de la red, el diseño de cada uno de los bloques funcionales que componen el sistema, el tipo de señal de medición que debe inyectarse a la red, las señales que deben medirse y adquirirse en el circuito, y el procesamiento y los cálculos necesarios para la obtención de resultados.

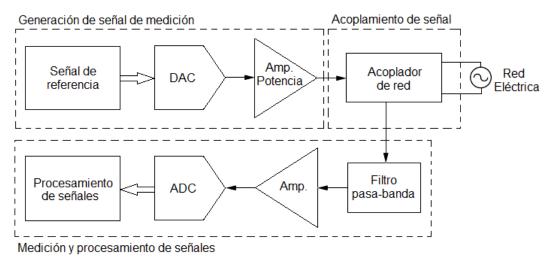

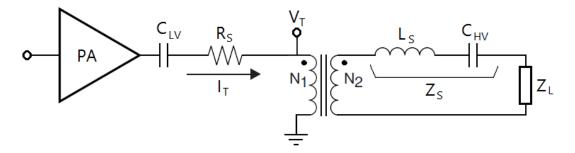

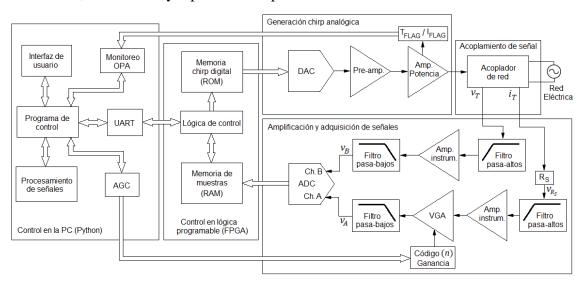

En el diagrama presentado en la Figura 2.1 se muestran los principales bloques funcionales que componen al sistema de caracterización de impedancia: un bloque de *generación de señal de medición*, responsable de generar una señal de referencia de banda angosta para su inyección a la red eléctrica; un bloque de *acoplamiento de señal*, compuesto por un acoplador de red adaptado para señales PLC de banda angosta; y un bloque de *medición y procesamiento de señales*, encargado de la adquisición y procesamiento digital de las señales requeridas para el cálculo de la impedancia de línea.

Figura 2.1: Diagrama en bloques del sistema.

## 2.1. Método de medición

El valor de una impedancia cualquiera a una determinada frecuencia puede obtenerse como la relación entre una señal de tensión, aplicada sobre la impedancia a la frecuencia correspondiente, y la señal de corriente que se produce, en consecuencia, sobre la misma:

$$Z(f) = \frac{V(f)}{I(f)} \tag{2.1}$$

En el caso particular del canal de comunicaciones sobre la red eléctrica, la impedancia que se desea caracterizar es aquella que ve el transmisor para una banda de frecuencia específica. Por lo tanto, para caracterizar la impedancia de la red se propone inyectar una señal que haga un barrido de frecuencia dentro de la banda de interés y al mismo tiempo realizar la medición y adquisición de muestras de las señales de tensión y corriente

producidas en el acoplador. De esta manera, mediante un posterior procesamiento digital de las mismas se podrá calcular la impedancia reflejada por el acoplador para luego, a partir de ésta, obtener la impedancia de carga presente en el punto de conexión a la red eléctrica. Este método de medición requiere conocer, entre otros parámetros, las características del circuito de acoplamiento usado ya que, como se verá más adelante, los elementos que lo componen determinan el valor de la impedancia reflejada y, en consecuencia, la forma en que debe calibrarse el sistema y los cálculos que se hacen para obtener el valor de la impedancia de línea en el punto de medición.

#### 2.2. Generación de la señal de medición

Por cuestiones de simplicidad en la implementación del sistema, la generación de la señal de barrido en frecuencia se hará digitalmente y sus muestras se almacenarán en una memoria dentro del sistema de control. Por lo tanto, será necesario utilizar un DAC que convierta la señal generada digitalmente en una señal analógica que pueda ser alimentada a la entrada del amplificador de potencia, para que finalmente sea inyectada a la red eléctrica a través del acoplador.

#### 2.2.1. Señal de barrido (chirp)

La medición de la impedancia de línea requiere inyectar una señal cuyo espectro de frecuencias abarque el ancho de banda sobre el que se desea caracterizar la misma. La forma más simple y práctica de hacerlo es inyectar una señal senoidal de amplitud fija y hacer un barrido de la frecuencia de la misma, comenzando por la frecuencia inferior y finalizando en la frecuencia superior de la banda. Una señal con estas características es conocida como *señal de barrido* o *chirp* [33], y se clasifica según la forma en que varía la frecuencia de la señal en relación con el tiempo. Para comprender mejor el comportamiento de una chirp, se hará un primero un análisis de la forma de onda de la señal en el dominio del tiempo y luego de su espectro en el dominio de la frecuencia.

Si la forma de onda de la señal se define como:

$$x(t) = \sin(\phi(t)) \tag{2.2}$$

entonces la frecuencia instantánea se define como la tasa de cambio de fase:

$$f(t) = \frac{1}{2\pi} \frac{d\phi(t)}{dt} \tag{2.3}$$

y la tasa de cambio de frecuencia instantánea (o chirpyness) se define como:

$$c(t) = \frac{1}{2\pi} \frac{d^2 \phi(t)}{dt^2} = \frac{df(t)}{dt}$$

(2.4)

En una *chirp lineal*, la frecuencia instantánea f(t) varía exactamente de forma lineal con el tiempo:

$$f(t) = f_0 + kt \tag{2.5}$$

donde  $f_0$  es la frecuencia inicial (para t = 0), y k la tasa de cambio de frecuencia o *chirpyness*, que se puede expresar como:

$$k = \frac{f_1 - f_0}{T} \tag{2.6}$$

donde  $f_1$  es la frecuencia final,  $f_0$  es la frecuencia inicial, y T es el tiempo que toma barrer desde la frecuencia inicial a la frecuencia final.

La función en el dominio de tiempo correspondiente para la fase de cualquier señal oscilante es la integral de la función de frecuencia, ya que se espera que la fase crezca como  $\phi(t + \Delta t) \cong \phi(t) + 2\pi f(t)\Delta t$ , es decir, que la derivada de la fase sea la frecuencia angular  $\phi'(t) = 2\pi f(t)$ . Luego, para la chirp lineal, esto resulta en:

$$\phi(t) = \phi_0 + 2\pi \int_0^t f(\tau) d\tau =$$

$$= \phi_0 + 2\pi \int_0^t (f_0 + k\tau) d\tau =$$

$$= \phi_0 + 2\pi \left( f_0 t + \frac{k}{2} t^2 \right)$$

(2.7)

donde  $\phi_0$  es la fase inicial (para t=0). Por lo tanto, también se la conoce como *señal de fase cuadrática*. En consecuencia, la correspondiente función en el dominio de tiempo para una chirp lineal senoidal es el seno de la fase  $\phi(t)$  en radianes:

$$x(t) = \sin\left[\phi_0 + 2\pi\left(f_0t + \frac{k}{2}t^2\right)\right]$$

(2.8)

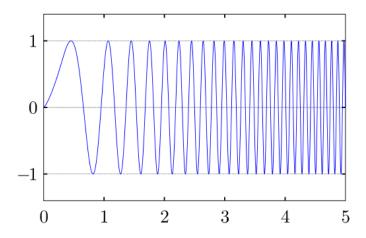

A modo de ejemplo, en la Figura 2.2 se muestra la forma de onda de una chirp lineal con  $\phi_0 = 0$ ,  $f_0 = 0.1$  y k = 2, para t = [0, 5].

Figura 2.2: Forma de onda de una chirp lineal; onda senoidal que aumenta en frecuencia linealmente con el tiempo [33].

El espectro de la chirp permite describir sus características en términos de sus componentes de frecuencia [34]. Esta representación en el dominio de frecuencia es una alternativa a la representación de la forma de onda en el dominio de tiempo, y las dos versiones están matemáticamente relacionadas por la transformada de Fourier. El espectro es de particular interés si la chirp está sometida a un posterior procesamiento de señal, ya que es posible determinar ciertos efectos no deseados atribuibles directamente a las características espectrales de la misma.

La forma más sencilla de derivar el espectro de una chirp es muestrear la forma de onda en el dominio del tiempo a una frecuencia superior al límite de Nyquist [35] y ejecutar un algoritmo de FFT [36] para obtener el resultado deseado. Sin embargo, un análisis analítico, cuando es posible, sigue siendo útil ya que proporciona una visión adicional al comportamiento y propiedades de las chirps.

Una expresión general para una forma de onda oscilatoria, centrada en la frecuencia  $\omega_0$ , es:

$$s(t) = a(t). e^{j[\omega_0 t + \theta(t)]}$$

(2.9)

donde a(t) y  $\theta(t)$  dan las variaciones de amplitud y fase de la forma de onda s(t) con el tiempo. El espectro de frecuencia de esta forma de onda se obtiene calculando la transformada de Fourier de s(t), es decir:

$$S(\omega) = \int_{-\infty}^{\infty} s(t) \cdot e^{-j\omega t} dt = \int_{-\infty}^{\infty} a(t) \cdot e^{j[(\omega_0 - \omega)t + \theta(t)]} dt \qquad (2.10)$$

En algunos casos especiales, la integral se puede resolver para dar una expresión analítica, pero a menudo las características de a(t) y  $\theta(t)$  son tales que la integral solo puede evaluarse mediante un algoritmo de aproximación o por integración numérica. En el caso especial en que a(t) se restringe a ser un pulso plano y donde la frecuencia instantánea varía como una función lineal de tiempo, entonces es posible una solución analítica. Por conveniencia, se considera que el pulso tiene amplitud unitaria y de duración T, con la amplitud y fase definidas durante el intervalo de tiempo -T/2 a +T/2. El barrido de frecuencia total es  $\Delta F$ , variando de forma lineal desde  $-\Delta F/2$  a  $+\Delta F/2$  en el intervalo de tiempo definido. Como se vio anteriormente, cuando la frecuencia es una función lineal en el tiempo, la fase es una función cuadrática y entonces s(t) se puede expresar como:

$$s(t) = 1. e^{j\left[\omega_0 t + \frac{\Delta\Omega}{2T}t^2\right]} \text{ donde } \Delta\Omega = 2\pi\Delta F \text{ y } -\frac{T}{2} < t < \frac{T}{2}$$

(2.11)

Entonces, el espectro de esta chirp lineal es:

$$S(\omega) = \int_{-T/2}^{T/2} e^{j\left[(\omega_0 - \omega)t + \frac{\Delta\Omega}{2T}t^2\right]} dt$$

(2.12)

Luego, al aplicar el método de *completar el cuadrado* [37] y recurrir a las *integrales* de Fresnel [38], C(X) y S(X), definidas por:

$$C(X) = \int_0^X \cos\left(\frac{\pi \cdot y^2}{2}\right) dy \quad \text{y} \quad S(X) = \int_0^X \sin\left(\frac{\pi \cdot y^2}{2}\right) dy$$

permite evaluar la expresión (2.12) para obtener el siguiente resultado:

$$S(\omega) = \sqrt{\frac{\pi \cdot T}{\Delta \Omega}} \cdot e^{-j \left[ (\omega - \omega_0)^2 \cdot \frac{T}{2 \cdot \Delta \Omega} \right] \cdot \left[ C(X_1) + jS(X_1) + C(X_2) + jS(X_2) \right]}$$

(2.13)

donde

$$X_1 = \frac{\frac{\Delta\Omega}{2} + (\omega - \omega_0)}{\sqrt{\frac{\pi\Delta\Omega}{T}}}$$

y  $X_2 = \frac{\frac{\Delta\Omega}{2} + (\omega_0 - \omega)}{\sqrt{\frac{\pi\Delta\Omega}{T}}}$

En este caso, se puede considerar que el espectro de la chirp lineal tiene tres componentes principales, a saber:

Un término de Amplitud,

$$|S(\omega)| = \sqrt{\frac{\pi \cdot T}{\Delta \Omega}} \cdot \left[ \left( C(X_1) + C(X_2) \right)^2 + \left( S(X_1) + S(X_2) \right)^2 \right]^{\frac{1}{2}}$$

(2.14)

Un término de Fase Cuadrática,

$$\Phi_1(\omega) = -\frac{T}{2.\Delta\Omega} \cdot (\omega - \omega_0)^2 \tag{2.15}$$

Un término de Fase Residual,

$$\Phi_2(\omega) = \arctan \left[ \frac{S(X_1) + S(X_2)}{C(X_1) + C(X_2)} \right]$$

(2.16)

La relación del argumento de  $\Phi_2(\omega)$  se aproxima a la unidad en una gran parte del rango de frecuencias de interés, por lo que  $\Phi_2$  se aproxima a una fase constante de  $\pi/4$  allí. Luego, si se introduce un factor de escala  $n=\frac{2(\omega-\omega_0)}{\Delta\Omega}$ , entonces las expresiones para los argumentos de Fresnel se pueden reescribir como:

$$X_1 = \frac{\sqrt{T \cdot \Delta F}}{\sqrt{2}} \cdot (1+n) \quad y \quad X_2 = \frac{\sqrt{T \cdot \Delta F}}{\sqrt{2}} \cdot (1-n)$$

(2.17)

Ahora, los espectros son funciones del producto  $T.\Delta F$ , independiente de cualquier valor particular de frecuencia central y ancho de banda. A este producto a menudo se lo conoce como el *producto tiempo-ancho de banda* de la chirp.

Se han publicado tablas de las integrales de Fresnel, junto con rutinas matemáticas para calcular las integrales manualmente o mediante un programa informático. Además, algunos programas de software matemáticos, como *Mathcad*, *MATLAB* y *Mathematica*,

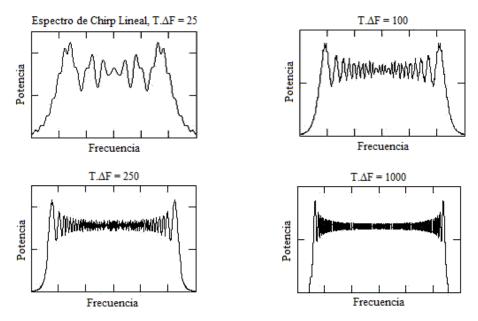

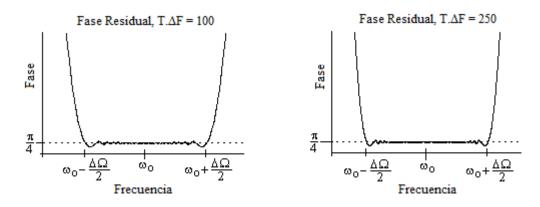

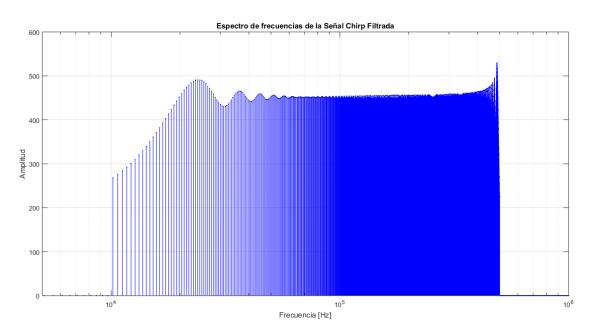

tienen rutinas incorporadas para evaluar las integrales, ya sea como funciones estándar o en paquetes de extensión. De esta forma, para visualizar y comprender mejor las características espectrales de una chirp lineal, en la Figura 2.3 se muestran algunos gráficos del espectro de potencia  $|S(\omega)|^2$  para productos  $T.\Delta F$  de 25, 100, 250 y 1000. Se observa que, cuando el producto es chico, las ondas de Fresnel son muy evidentes pero el espectro tiende a un perfil más rectangular para valores más grandes.

Figura 2.3: Espectros de potencia de una chirp lineal [34].

En el caso de los gráficos de fase residual  $\Phi_2(\omega)$ , los perfiles tienden a ser muy similares en un amplio rango de productos tiempo-ancho de banda. Dos ejemplos, para  $T.\Delta F = 100$  y 250, se muestran en la Figura 2.4. Como se mencionó anteriormente, se observa que tienen una fase cercana a un valor de  $\pi/4$  dentro del rango  $\omega_0 \pm \Delta\Omega/2$ .

Figura 2.4: Fase residual de una chirp lineal [34].

En consecuencia, para frecuencias en el rango de barrido, es el término de fase cuadrática  $\Phi_1(\omega)$ , independiente del valor del producto tiempo-ancho de banda, el que es de mayor interés. Si bien el término de fase residual agrega perturbaciones menores a la fase total de la chirp dentro del rango de barrido, a frecuencias por fuera de ese rango,

$\Phi_2(\omega)$  se desvía rápidamente de  $\pi/4$ , por lo que la fase total se desvía seriamente de una característica cuadrática allí.

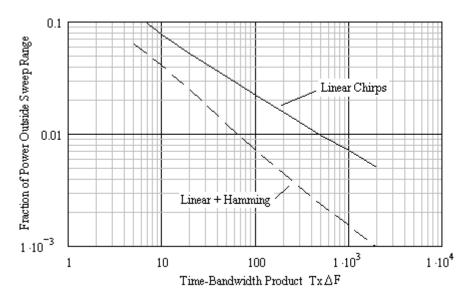

Afortunadamente, como se observa en el gráfico de la Figura 2.5, hay muy poco contenido espectral más allá del rango de frecuencia de barrido de una chirp y esto es especialmente cierto para las formas de onda donde el producto tiempo-ancho de banda es grande. Para chirps lineales, los resultados muestran que sólo un 2% de la potencia total reside por fuera de  $\Delta F$  cuando  $T.\Delta F$  es 100, y es menor al 1% cuando  $T.\Delta F$  es mayor a 500. En el caso de una chirp no-lineal, o una chirp lineal modulada en amplitud, la fracción de potencia por fuera de  $\Delta F$  es incluso menor, como se muestra en el gráfico para espectros con un perfil de Hamming. Esta reducida dispersión espectral es particularmente significativa cuando estas señales deben digitalizarse, ya que permite elegir una frecuencia de muestreo que sea solo ligeramente mayor que el doble de la máxima frecuencia de excursión de la chirp.

Figura 2.5: Fracción de potencia de una chirp por fuera del rango de barrido [34].

El procedimiento para generar una versión digital de la chirp lineal requiere que la función de la expresión (2.11), correspondiente a la forma de onda de la señal en el tiempo, sea muestreada a intervalos igualmente espaciados. Una consecuencia del muestreo es que el espectro resultante es periódico en el dominio de la frecuencia. Además del espectro de banda de base (deseado), se producen versiones adicionales del espectro, centradas en múltiplos de la frecuencia de muestreo. Para asegurar que no haya superposición de frecuencias, es decir que no se produzca "aliasing", debe cumplirse el teorema de muestreo de Nyquist [39]. En la práctica, es aconsejable una frecuencia de muestreo sustancialmente más alta que la dictada por el teorema.

El espectro de una señal muestreada se puede obtener aproximando, por un método de integración numérica, la integral de la transformada de Fourier. Generalmente, el método supone que el valor de la señal para una muestra tomada en un instante de tiempo permanece constante durante un intervalo de muestreo, hasta que se toma la siguiente muestra. Este procedimiento es denominado como *muestreo y retención de orden cero*. Si el intervalo de tiempo entre muestras es  $T_s$ , entonces  $s_n = s(nT_s)$ , y la integral deseada

se obtiene, aproximadamente, al sumar las áreas rectangulares. El resultado así obtenido es la convolución de un pulso rectangular, con un tamaño de escalón  $T_s$ , con los impulsos ubicados en los instantes de muestreo, con pesos iguales a los valores de muestra  $s_n$ . En consecuencia, el espectro de interés tendrá superpuesta la respuesta de frecuencia de la función de muestreo y retención de orden cero, de modo que el espectro de la señal muestreada viene dado por:

$$S_s(\omega) = T_s \frac{\sin(\omega T_s/2)}{\omega T_s/2} \cdot \left[ \sum_{n=-\infty}^{\infty} s_n e^{-j(n\omega T_s)} \right]$$

(2.18)

El primer término de la expresión es la respuesta en frecuencia del muestreo y retención de orden cero, cuya amplitud disminuye con la frecuencia y cae al 63% de su valor pico a la mitad de la frecuencia de muestreo y es cero en los múltiplos de esa frecuencia, ya que  $f_s = 1/T_s$ . El segundo término de la expresión corresponde a la transformada de Fourier de la señal discreta  $s_n$ . Es una función continua sobre todo  $\omega$  e implica un número infinito de sumas. En la práctica, el proceso de suma puede truncarse a un número finito de muestras N, cuando la forma de onda es periódica o cero fuera del rango de muestras. Además, dado que el mismo espectro se repite infinitamente, es posible limitar el interés a las componentes espectrales dentro del rango  $-f_s/2$  a  $f_s/2$ .

Si limitamos el interés en el espectro calculado a un número finito de puntos de datos discretos *N*, en las frecuencias dadas por:

$$\omega_k = \frac{2\pi k}{NT_s}$$

para  $k = 0, 1, 2, ..., (N-1)$  (2.19)

entonces la fórmula para calcular la transformada discreta de Fourier [40] de la señal muestreada es:

$$S_k = S(\omega_k) = \sum_{n=0}^{N-1} s_n e^{-j\left(\frac{2\pi kn}{N}\right)}$$

(2.20)

Los cálculos para la expresión anterior se pueden llevar a cabo por medio de un algoritmo de cálculo directo, pero esto no es muy eficiente en el uso de recursos. En consecuencia, se han desarrollado algoritmos más eficientes, especialmente las transformadas rápidas de Fourier (FFT) [36]. Programas informáticos de código abierto que implementan la FFT están ampliamente disponibles, y también se incorporan en funciones estándar de programas de software matemáticos como, por ejemplo, MATLAB.

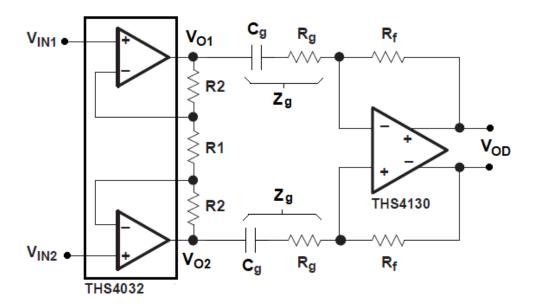

#### 2.2.2. Conversor digital-analógico (DAC)

La elección del DAC se hace básicamente teniendo en cuenta la frecuencia de muestreo que se usará para generar la señal chirp digital y la resolución en amplitud que se quiere obtener en la señal chirp analógica a la salida del conversor. Se elige usar un

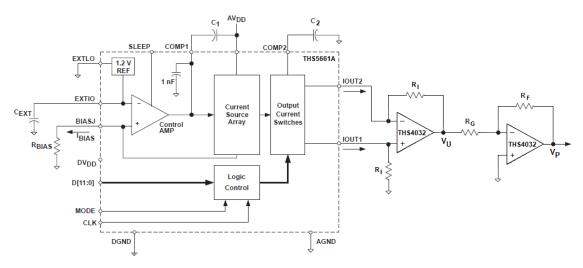

DAC THS5661A de Texas Instruments [31], que posee una resolución de 12 bits y salidas complementarias de corriente, pudiendo configurar mediante una resistencia externa la corriente de salida a fondo de escala. Para una tensión de alimentación digital de 3,3V el DAC puede operar a una frecuencia de muestreo máxima de 70 MSPS. En la Figura 2.6 se muestra el esquema utilizado para la conversión, que incluye el diagrama en bloques funcional del DAC, el circuito necesario para generar la señal de tensión a partir de las salidas de corriente complementarias del DAC, y un pre-amplificador para obtener la amplitud de señal requerida a la entrada del amplificador de potencia.

Figura 2.6: Esquema de conversión de señal digital a señal analógica.

El THS5661A genera corrientes de salida complementarias en IOUT1 e IOUT2. La corriente de salida IOUT1 es igual a la corriente de salida a fondo de escala, IOUT<sub>FS</sub>, cuando todos los bits de entrada están en alto en el modo 0 (formato binario), es decir, la palabra de entrada binaria tiene la representación decimal 4095. De forma complementaria, IOUT<sub>FS</sub> circulará a través del terminal IOUT2 cuando todos los bits de entrada estén bajos en el modo 0 (formato binario), es decir, la palabra de entrada binaria tiene la representación decimal 0. De este modo, las corrientes de salida pueden expresarse como:

$$IOUT1 = IOUT_{FS}.\frac{CODE}{4096} \tag{2.21}$$

$$IOUT2 = IOUT_{FS} \cdot \frac{(4095 - CODE)}{4096} \tag{2.22}$$

donde CODE es la representación decimal de la palabra de entrada binaria de datos del DAC. La corriente de salida a fondo de escala se ajusta usando una resistencia externa R<sub>BIAS</sub>. La corriente base, I<sub>BIAS</sub>, a través de la resistencia R<sub>BIAS</sub> está definida por el amplificador de control y la tensión de referencia usada. La corriente de salida a fondo de escala es igual a 32 veces esta corriente base. La corriente de salida IOUT<sub>FS</sub> puede, entonces, expresarse como:

$$IOUT_{FS} = 32.I_{BIAS} = \frac{32.V_{EXTIO}}{R_{BIAS}}$$

(2.23)

donde  $V_{EXTIO}$  es la tensión en el terminal EXTIO. La tensión de referencia interna proporciona una tensión precisa de 1,2V. Esta referencia está presente en el terminal EXTIO cuando el terminal EXTLO está conectado a AGND. Un capacitor de desacoplamiento externo  $C_{EXT}$  de 0,1  $\mu F$  debe ser conectado externamente al terminal EXTIO para compensación. Usando la referencia interna, la corriente IOUT<sub>FS</sub> puede ajustarse entre 20 mA y 2 mA, simplemente variando el valor de la resistencia  $R_{BIAS}$  entre 1,92  $k\Omega$  y 19,2  $k\Omega$ .

Los nodos de salida IOUT1 e IOUT2 tienen una máxima tensión negativa de operación de -1V, determinada por el proceso CMOS, que no debe superarse para evitar daños al dispositivo. La máxima tensión positiva de operación de las salidas depende de la corriente de salida a fondo de escala IOUT<sub>FS</sub> y de la tensión de alimentación positiva A<sub>VDD</sub>. Esta tensión es igual a 1,25 V para AVDD = 5 V e IOUT<sub>FS</sub> = 20 mA. Exceder la tensión positiva afecta adversamente el rendimiento de distorsión y la no linealidad integral. El rendimiento de distorsión óptimo para una salida unipolar o diferencial se logra cuando la máxima señal a fondo de escala en IOUT1 e IOUT2 no excede de 0,5 V.

Luego, para realizar la conversión de la señal de salida de corriente diferencial a tensión unipolar, que permita alimentar la entrada del pre-amplificador, se utiliza un amplificador operacional de tensión THS4032 de Texas Instruments [32] dispuesto en una configuración I-V (corriente-tensión). La transferencia de esta etapa es la siguiente:

$$G_{I-V} = \frac{V_U}{(I_{OUT1} - I_{OUT2})} = R_I \tag{2.24}$$

En consecuencia, la tensión máxima en los nodos de salida, IOUT1 e IOUT2, será igual a:

$$V_{OUT1(max)} = V_{OUT2(max)} = IOUT_{FS}.R_I$$

(2.25)

que como se mencionó anteriormente se debe asegurar que sea menor o igual a 0,5 V para obtener un rendimiento de distorsión óptimo en las salidas del DAC.

Para la última etapa del circuito se emplea también un amplificador operacional de tensión THS4032 en configuración inversora, por lo que su ganancia será:

$$G_P = \frac{V_P}{V_U} = -\frac{R_F}{R_G} \tag{2.26}$$

y cuyo valor dependerá de la amplitud de señal requerida a la entrada del amplificador de potencia.

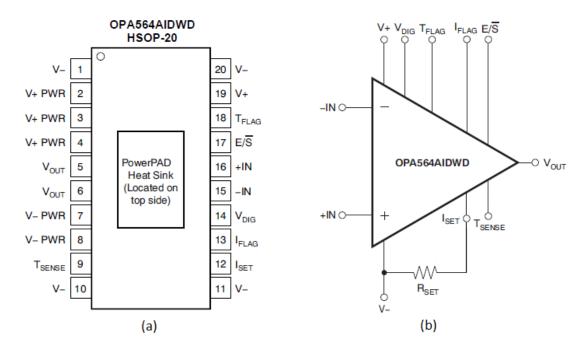

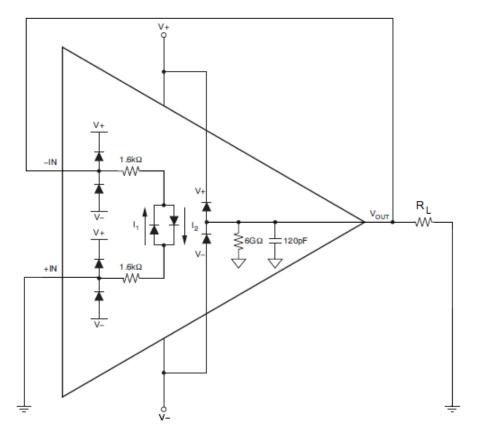

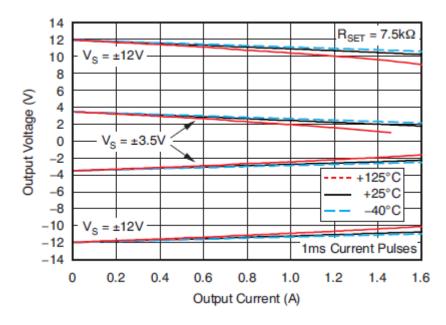

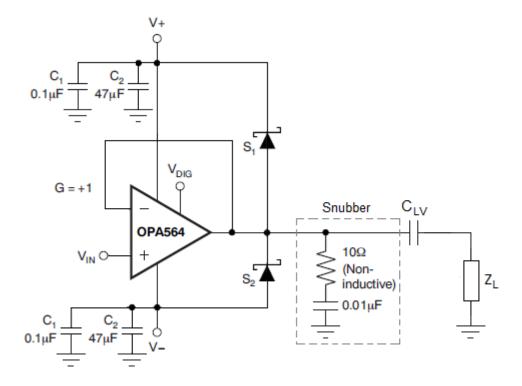

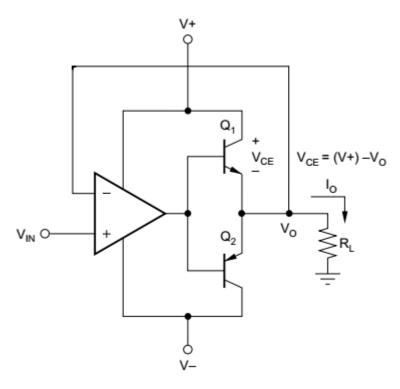

#### 2.2.3. Amplificador de potencia

La elección del amplificador de potencia se hace en base al rango de tensión de salida, la capacidad de corriente de salida y el ancho de banda de frecuencias, requeridos para una adecuada inyección de señal en la red. Para determinar la capacidad de corriente de salida necesaria, primero se debe tener una idea aproximada de la impedancia de carga conectada a la salida del acoplador. Como se mencionó en la Sección 1.4.2, estudios previos hechos sobre la red eléctrica de baja tensión muestran que la impedancia puede ser tan baja como 1 Ω. Teniendo en cuenta esto y las características del acoplador, se utilizará un amplificador de potencia OPA564 de Texas Instruments [30] que está diseñado para ser usado en aplicaciones PLC de banda angosta. Posee una capacidad máxima de corriente de salida de 1,5 A (dc o rms) sobre cargas reactivas, un amplio rango de tensión de alimentación de ±3,5 V hasta ±12 V, y un ancho de banda de potencia total (Full-power Bandwidth) de 1,3 MHz. Además, este amplificador está internamente protegido contra condiciones de sobre-temperatura y sobrecargas de corriente, lo que implica una mayor confiabilidad en la etapa de potencia.

Figura 2.7: Amplificador OPA564 - (a) configuración de pines, (b) diagrama funcional.

El amplificador utiliza un encapsulado HSOP que posee un pad térmico (PowerPAD) que mejora significativamente la capacidad de disipación térmica del dispositivo (ver Figura 2.7-a). El pad puede estar ubicado en la parte inferior para ser soldado directamente a un plano de cobre en el PCB o en la parte superior para que pueda colocarse sobre el mismo un disipador de calor. El modelo elegido posee este pad térmico en la parte superior, simplificando el diseño del PCB y permitiendo la colocación de un disipador adecuado en base a la potencia máxima que se debe disipar.

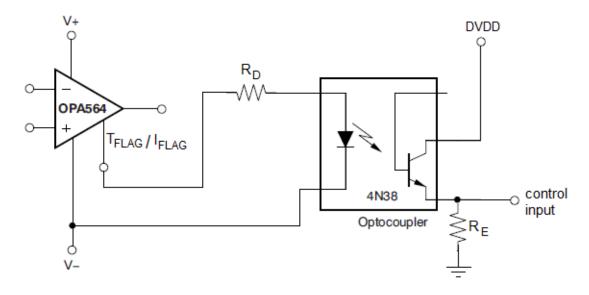

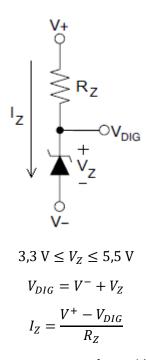

Otras características importantes del amplificador elegido son (ver Figura 2.7-b):

- posee alimentación digital (V<sub>DIG</sub>) de +3,3 V a +5,5 V referenciada al pin V-.

- su salida puede ser encendida o apagada por medio de una señal de control  $(E/\overline{S})$ .

- el límite de corriente de salida (I<sub>LIM</sub>) se puede establecer por medio del valor de una resistencia (R<sub>SET</sub>) conectada entre el pin I<sub>SET</sub> y V-.

dispone de dos señales de monitoreo, una indica si se alcanzó el límite de temperatura de operación (T<sub>FLAG</sub>) y la otra indica si se alcanzó el límite de corriente establecido (I<sub>FLAG</sub>).

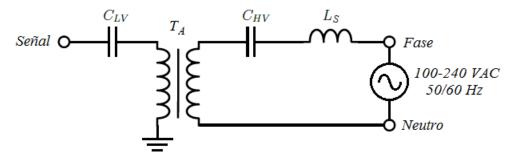

# 2.3. Acoplador de red

Uno de los componentes más críticos de un sistema PLC es el circuito de acoplamiento con la red eléctrica. Considerando la presencia de alta tensión, impedancias variables, y perturbaciones de gran amplitud que también son variantes en el tiempo, el circuito de acoplamiento se debe diseñar cuidadosamente de manera de proveer el ancho de banda y los niveles de protección adecuados.

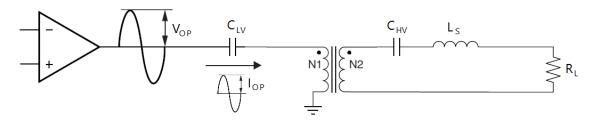

El circuito de acoplamiento tiene dos funciones principales, la primera es eliminar la componente fundamental (50 o 60 Hz) y los armónicos de la señal de alta tensión de línea de manera de proteger el circuito de baja tensión, y la segunda es permitir el acoplamiento de señales de alta frecuencia en la red [27]. Un circuito simplificado de un acoplador de red capacitivo usado típicamente en las aplicaciones de este tipo se muestra en la Figura 2.8. El capacitor de baja tensión (C<sub>LV</sub>) permite acoplar la señal de salida de alta frecuencia del amplificador de potencia al transformador de acoplamiento. El capacitor de alta tensión (C<sub>HV</sub>) bloquea la componente de baja frecuencia de la red eléctrica formando un divisor de tensión con la inductancia del transformador de acoplamiento. El inductor (L<sub>S</sub>) conectado en serie con el capacitor tiene la función de bajar la impedancia de salida del filtro, lo que permite la inyección de señales aún con baja impedancia de red. El transformador de acoplamiento (T<sub>A</sub>) tiene como función acoplar ambos extremos del circuito, y proveer aislación galvánica entre la zona de baja tensión y la zona de alta tensión del acoplador.

Figura 2.8: Circuito simplificado de acoplador PLC capacitivo.

El capacitor C<sub>LV</sub> debe tener una capacidad lo suficientemente grande de modo de tener una baja impedancia en toda la banda de frecuencias de interés. Además, la tensión de operación del capacitor debe ser tal que soporte la máxima tensión presente a la salida del amplificador de potencia; por lo que típicamente el valor usado será igual o ligeramente superior a la tensión de alimentación del amplificador. Para el caso del capacitor C<sub>HV</sub> se recomienda utilizar un capacitor de supresión de interferencia electromagnética y de interferencia de radiofrecuencia (EMI/RFI) de polipropileno metalizado debido al bajo factor de pérdida asociado con el dieléctrico, lo que resulta en un auto-calentamiento interno mínimo. Operar el capacitor en aproximadamente el 80%

de su tensión nominal garantiza una larga vida útil del componente, por lo que para una red eléctrica de 220 VAC es recomendable usar un capacitor con una tensión nominal de operación de 275 VAC. El valor de capacidad requerido dependerá del valor elegido para los demás componentes que se encuentran conectados en serie.

#### 2.3.1. Filtro de salida

Para tener una óptima inyección de señal a la red, la frecuencia central o de resonancia del filtro pasa-banda formado por C<sub>HV</sub> en serie con L<sub>S</sub> debe ser tal que se logre una adecuada simetría en la transferencia del filtro dentro de la banda de interés. El valor de la frecuencia central del filtro se calcula como:

$$f_c = \frac{1}{2\pi\sqrt{C_{HV}.L_S}} \tag{2.27}$$

Luego, para lograr la simetría de banda mencionada, la frecuencia central elegida debe ser igual a la media logarítmica de la banda de frecuencias usada, que se puede calcular como:

$$f_c = 10^{\frac{\log f_i + \log f_s}{2}} \tag{2.28}$$

donde  $f_i$  es la frecuencia inferior de la banda y  $f_s$  es la frecuencia superior de la banda. Una vez calculado el valor de  $f_c$  con la ecuación anterior es posible elegir los valores de  $C_{HV}$  y  $L_S$  que cumplan con este requisito. Se debe considerar además que el inductor  $L_S$  usado esté dimensionado para soportar la corriente de carga máxima sin saturación.

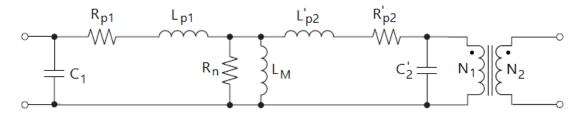

#### 2.3.2. Transformador de acoplamiento

La mayoría de los transformadores de acoplamiento para PLC son compactos, con relaciones de vueltas entre 1:1 y 4:1, baja inductancia de pérdidas y una inductancia de bobinado de unos pocos milihenries. El divisor de tensión formado por el capacitor  $C_{HV}$  y esta inductancia de bobinado es el encargado de reducir la tensión de red a niveles despreciables en la salida del amplificador de potencia. En un circuito de acoplamiento típico, la tensión de red inyectada en la salida del amplificador de potencia es de aproximadamente  $20 \text{ mV}_{pp}$ , aunque puede tolerarse un mayor valor mientras no afecte el normal funcionamiento del circuito.

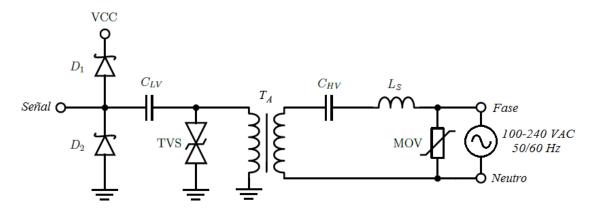

Determinar la relación de vueltas  $(N_1/N_2)$  óptima para el transformador de acoplamiento es simple, se basa en el principio de usar la máxima capacidad de tensión de salida junto con la máxima capacidad de corriente de salida del amplificador de potencia para lograr la máxima eficiencia de transferencia de potencia a la carga. Suponiendo que el rango de tensión de salida, la máxima corriente de salida y la impedancia de carga son conocidas, la relación de vueltas para el circuito de la Figura 2.9 se calcula a partir de las siguientes ecuaciones:

$$\frac{V_{OP}}{I_{OP}} = R_L \cdot \left(\frac{N_1}{N_2}\right)^2 \tag{2.29}$$

$$\frac{N_1}{N_2} = \sqrt{\frac{V_{OP}}{I_{OP}.R_L}} \tag{2.30}$$

Figura 2.9: Circuito de acoplamiento PLC.

Si la relación de vueltas se selecciona para ser mayor que el valor ideal, la salida total del circuito es entonces limitada por la capacidad de tensión de salida del amplificador de potencia. Si la relación de vueltas es seleccionada para ser menor que el valor ideal, la salida queda limitada por la máxima corriente de salida del amplificador de potencia. Si se utiliza la relación de vueltas ideal, la salida máxima se produce cuando el amplificador se acerca tanto a su máxima tensión de salida como a su máxima corriente de salida. Esta condición da como resultado la máxima eficiencia de transferencia de potencia a la carga.

### 2.3.3. Dispositivos de protección

La red eléctrica es un ambiente severo para los componentes electrónicos. Ruido o perturbaciones de gran amplitud, causadas por relámpagos, descargas de bancos de capacitores, conmutaciones inductivas u otras fallas pueden dañar los componentes electrónicos del sistema si no están debidamente protegidos. Por lo tanto, para su implementación práctica, al circuito de la Figura 2.8 se le deben añadir dispositivos de protección como:

- Varistores de óxido metálico (MOV), para proteger contra sobretensiones transitorias de la red.

- Diodos de supresión de transitorios de voltaje (TVS), como protección contra los transitorios de conexión a la red.

- Diodos de enclavamiento, para proteger contra sobretensiones en la señal de entrada.