# Diseño e Implementación de Generador de Señal BPSK con Parámetros Regulables

Trabajo final presentado como requisito para la obtención del título de grado de Ingeniero Electrónico

Autor: Sr. Mariano Damián Morel

Dr. Ing. Luciana De Micco Director Ing. Lucas Rabioglio Co-director

3 de octubre de 2022

Laboratorio de Sistemas Caóticos

Departamento de Ingeniería Electrónica y Computación Facultad de Ingeniería Universidad Nacional de Mar del Plata Argentina

RINFI se desarrolla en forma conjunta entre el INTEMA y la Biblioteca de la Facultad de Ingeniería de la Universidad Nacional de Mar del Plata.

Tiene como objetivo recopilar, organizar, gestionar, difundir y preservar documentos digitales en Ingeniería, Ciencia y Tecnología de Materiales y Ciencias Afines.

A través del Acceso Abierto, se pretende aumentar la visibilidad y el impacto de los resultados de la investigación, asumiendo las políticas y cumpliendo con los protocolos y estándares internacionales para la interoperabilidad entre repositorios

Esta obra está bajo una <u>Licencia Creative Commons Atribución-</u>

NoComercial-CompartirIgual 4.0 Internacional.

# Diseño e Implementación de Generador de Señal BPSK con Parámetros Regulables

Trabajo final presentado como requisito para la obtención del título de grado de Ingeniero Electrónico

Autor: Sr. Mariano Damián Morel

Dr. Ing. Luciana De Micco Director Ing. Lucas Rabioglio Co-director

3 de octubre de 2022

Laboratorio de Sistemas Caóticos

Departamento de Ingeniería Electrónica y Computación Facultad de Ingeniería Universidad Nacional de Mar del Plata Argentina

## Agradecimientos

No ha sido sencillo llegar a este punto, y estoy convencido de que no lo podría haber hecho solo. Sin dudas es un momento muy importante para mí, soñado, y que afortunadamente puedo compartir con las personas que quiero. Esta primera página da en parte sentido a las páginas siguientes y con el corazón es un gracias infinito.

A mis padres mentores de la vida, cuyos valores y ejemplos son incalculables, su acompañamiento amor y bondad me hacen ser un hombre justo y completo. Los amo, y agradezco a la vida por tenerlos conmigo.

A toda mi familia, mis hermanos y sus parejas, sobrinos, primos y a mi tía por tener un pedazo de ser de cada uno de ellos, en mi impronta y personalidad.

A los que ya no están físicamente, pero me acompañan a diario, mi tío Carlos y mi abuela Assunta, quienes fueron personas fuera de serie.

A mis amigos, mi otra familia, quienes están siempre, apoyando, alentando, quienes se alegran por cada logro.

A los que ya no están por cosas de la vida, que tuvieron un paso en algún momento determinado y que han acompañado y apoyado, los recordaré con cariño.

A todas esas personas que aparecieron recientemente por regalo de la vida y que brindan toda su paciencia y su tiempo acompañándome.

A la Dra. Luciana De Micco, directora de mi proyecto final, a quien debo mencionar especialmente, quien desde el inicio de este trabajo, se convirtió en una fuente inagotable de motivación, aliento, paciencia y conocimiento en momentos donde el camino se tornaba con escollos. A todo el laboratorio de Sistemas Caóticos, los ingenieros Maximiliano Antonelli, Juan Pablo Barrangú, Raúl Lopresti y al Co-director de mi proyecto, Lucas Rabioglio, quienes estuvieron desde el primer día aportando su granito de arena. Es un sincero gracias, aunque cualquier palabra de agradecimiento hacia ustedes quedará pequeña. Por fortuna, me tocó estar en el lugar, momento y con las personas correctas, imposible pedir más.

Por último a aquellos docentes (y educadores) de los diferentes años que con sus palabras y ayuda que atesoro, las recuerden o no, me han conducido a este hermoso momento: Rogelio García Retegui, Gustavo Meschino, Carolina Di Benedetto, Graciela Fernandez, Claudio González, Virginia Ballarín, Guillermo Abras y Jorge Petrillo. A todos los docentes, no docentes, compañeros de la carrera y a la Facultad de Ingeniería de la UNMdP en general, gracias!.

#### Resumen

En este trabajo se diseñó e implementó un generador de señal modulada en fase. El circuito se implementó mediante una FPGA (Field Programmable Gate Array) y un conversor digital analógico (DAC). El sistema desarrollado permite recibir los datos a través de una entrada externa o los genera en forma interna mediante un generador de números pseudo aleatorios (PRNG). El diseño permite variar en un gran rango la cantidad de ciclos de portadora por dato y la frecuencia de portadora, así como la potencia de salida. El circuito utiliza una mínima cantidad de recursos de la FPGA gracias a la implementación de la portadora mediante el almacenamiento de un cuarto de ciclo y su correspondiente lógica de lectura.

Palabras clave – Modulación de fase, FPGA, DAC, BPSK, PRNG.

#### Abstract

In this work, a phase modulated signal generator was designed and implemented. The circuit was implemented using a FPGA (Field Programmable Gate Array) and a digital analog converter (DAC). The developed system allows data to be received through an external input or generated internally through a pseudo random number generator (PRNG). The design allows the number of carrier cycles per data and the carrier frequency, as well as the output power, to be varied over a wide range. The circuit uses a minimum amount of FPGA resources thanks to the implementation of the carrier by storing a quarter cycle and its corresponding read logic.

Keywords - Phase modulation, FPGA, DAC, BPSK, PRNG.

# Índice general

| т.        | Introduction                                               | ٤   |

|-----------|------------------------------------------------------------|-----|

| 2.        | Anteproyecto  2.1. Requerimientos y aspectos constructivos |     |

| 3.        | Proyecto                                                   | 15  |

|           | 3.1. Primera etapa: Circuito implementado en FPGA          |     |

|           | 3.1.1. Bloques del proceso                                 |     |

|           | 3.2. Segunda etapa: Circuito conversor digital/analógico   |     |

|           | 3.2.1. Funcionamiento circuital                            |     |

|           | 3.2.2. Diseño de la placa                                  |     |

|           | 3.3. Integración y testeos                                 | 30  |

| 4.        | Conclusiones                                               | 33  |

|           | 4.1. Resultados finales                                    | 33  |

|           | 4.2. Experiencias de la gestión del proyecto               |     |

| <b>5.</b> | Bibliografía                                               | 35  |

| Aı        | péndice                                                    | 37  |

| Α.        | Plan de Proyecto                                           | 39  |

| В.        | Especificación de Requerimientos                           | 49  |

| C.        | Especificación Funcional                                   | 69  |

| D.        | Especificación Técnica                                     | 83  |

| Е.        | Plan de pruebas                                            | 101 |

### Capítulo 1

### Introducción

Este trabajo es parte de un proyecto mayor en el que se pretende desarrollar sensores espectrales para Radio Cognitiva (RC) [1]. La técnica llamada Radio Cognitiva surge a partir de la saturación de los canales necesarios para realizar las comunicaciones. Como la utilización del espectro por parte de los licenciatarios no es continua en cuanto a frecuencia, tiempo y espacio, RC permite que usuarios secundarios utilicen el espectro ocioso. Por esto, el sensado espectral para determinar si el canal se encuentra libre u ocupado es central. Estos sensores deben ser capaces de detectar la presencia de señal modulada en situaciones de relación de señal a ruido muy bajas. En este contexto, es necesario contar con un generador que entregue señales moduladas y permita realizar variaciones en cuanto a potencia, frecuencia de portadora y velocidad de datos, entre otras.

Existen trabajos en los que se proponen diseños en FPGA de moduladores BPSK (modulación binaria de fase). En estos trabajos no se encontraron implementaciones con flexibilidad en los parámetros de la transmisión, tales como variación de frecuencia de portadora, cantidad de ciclos de portadora por dato, frecuencia de dato y potencia de salida en tiempo de ejecución. En [2] los autores realizan la simulación de la parte digital de un transmisor BPSK. Allí se almacenan en LUTs (Look Up Tables) 13 muestras de un período de una señal sinusoidal, y obtienen una frecuencia de portadora de 50 MHz. Proponen enviar la señal modulada digital en forma serie mediante Serial Peripheral Interface (SPI) al DAC embebido en la placa de desarrollo Spartan 3. Esto limita la máxima frecuencia de portadora.

En [3] los autores utilizan el entorno System Generator de Matlab de la empresa Xilinx para hacer el diseño de un modulador BPSK. La señal de portadora es implementada mediante un bloque Direct Digital Synthesis Compiler, almacenan en dos memorias ROMs (Read-Only Memory) dos ciclos de señal sinusoidal en contrafase. La implementación la realizan en dos placas Spartan 3E Starter Kit. Obtienen una frecuencia de portadora 31, 250 KHz.

En [4] el diseño es también realizado mediante el entorno System Generator. Para la implementación utilizan una FPGA Virtex-4 de Xilinx. Generan la portadora almacenando 20 muestras de un ciclo de sinusoidal en una memoria ROM que actúa como LUT, cada dato se representa con 16 bits en aritmética de punto fijo con signo (14 bits fraccionarios). La cantidad de ciclos por dato es fija en uno, con una portadora de 5 MHz.

Para lograr la flexibilidad requerida, en este trabajo se realizó un diseño que almacena en memoria una gran cantidad de muestras de portadora. Luego, a través de entradas, se seleccionan las muestras a ser leídas y entregadas a un DAC que las recibe en forma paralela. Este conversor se encarga de generar la señal analógica de salida. La implementación desarrollada utiliza una mínima cantidad de recursos gracias a la arquitectura mejorada que aprovecha el almacenamiento interno de un cuarto de señal sinusoidal para generar la señal de portadora.

### Capítulo 2

# Anteproyecto

A continuación, se presentarán sucesivamente secciones con el detalle correspondiente en materia de requerimientos y constructivas tanto para software y hardware. Para ahondar respecto a especificaciones de requerimientos, funcionales y técnicas, el presente informe presenta al final un apartado **Apéndice** de tales documentos elaborados en forma previa, así mismo el plan de proyecto elaborado.

### 2.1. Requerimientos y aspectos constructivos

Esta implementación posee requisitos fundamentales tales como:

- Capacidad de almacenar en la ROM N cantidad de puntos de sinusoidal (N muestras de wl bits cada una).

- Distintas precisiones para los cálculos internos (cantidad de bits wl).

- El número de bits del DAC debe determinar el ancho de palabra de la señal de salida.

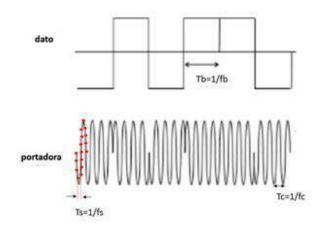

- Ts debe ser el período de muestreo (período de señal de salida de la FPGA que ingresa al DAC).

- Tb debe ser el tiempo de dato.

- Tc debe ser el período de la portadora.

- Poder ajustar el Nivel de SNR.

- El dato a transmitir que se va a implementar con un generador pseudoaleatorio.

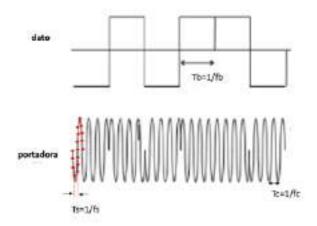

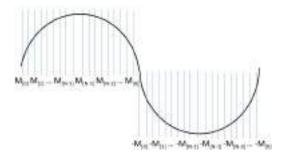

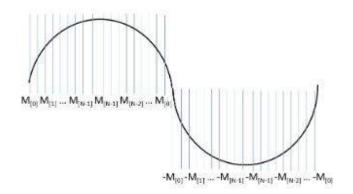

El dato a transmitir se va a implementar con un generador pseudoaleatorio, un ciclo de la señal de portadora debe almacenarse en una memoria ROM con N muestras de wl bits cada una, de tal manera que la memoria debe tener un tamaño de de N.wl. Los datos a trasmitir son de frecuencia fb, y la portadora fc. Nc es la cantidad de periodos de portadora que entran en un dato. La señal modulada se encuentra muestreada a una frecuencia fs. Los distintos parámetros mencionados se ven en la figura 2.1.

Como primera aproximación en lo que se requiere, se debe cumplir que

- Tb=Nc.Tc

- Tc=N.Ts

- Tb=Nc.N.Ts

Por otra parte la placa DAC debe tener la capacidad de poder convertir una cantidad de wl bits de modo de poder representar cada muestra de la señal senoidal que se almacene en la ROM. Tal conversor debe tener la función de variar su tensión de referencia, de manera de poder controlar la potencia de salida del DAC, para las mediciones correspondientes. Si bien a priori su conexión con la FPGA se haría mediante cable plano, en el transcurso del proyecto se optó por una conexión con un conector montado sobre la placa. Esto queda debidamente justificado para evitar cualquier tipo de ruido adicional sobre la señal de salida y ante cualquier daño que pueda sufrir el cable plano producido por uso o movimiento del mismo, de igual manera para evitar cualquier golpe en la placa DAC. Más detalles son descriptos en el **Apéndice** donde se detallan las especificaciones funcionales y técnicas del proyecto.

Figura 2.1: Señal modulante y muestreo de señal modulada

### 2.2. Alternativas de implementación de modulación BPSK

Con el objetivo de generar una implementación en la que se utilicen la menor cantidad de recursos respecto al uso de la placa FPGA, se analizaron dos alternativas posibles:

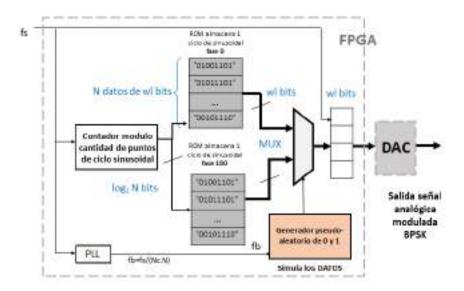

- La primera solución de diseño sería multiplexar una cantidad de palabras que representen un período de señal senoidal con fase 0 grados y otra de fase 180 grados. El orden de aparición se encuentra controlado por una generador pseudoaleatorio de datos binarios, tal como se puede ver en la figura 2.2.

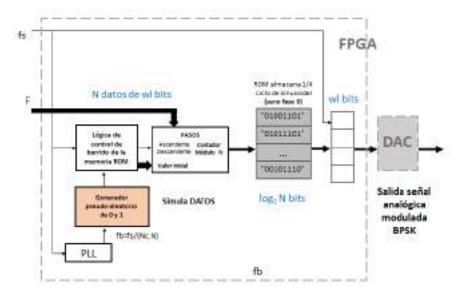

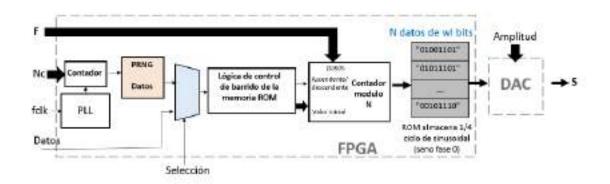

- Una optimización de este método se muestra en la **figura 2.3**, donde se va a almacenar solo un cuarto de un periodo de señal senoidal, bajo una lógica de control para el barrido de la misma, de manera de poder controlar la fase de la señal con la ventaja de utilizar menos cantidad de memoria.

Figura 2.2: Alternativa 1 - Cambio de fase con MUX

Figura 2.3: Alternativa 2 - Cambio de fase con lógica de control

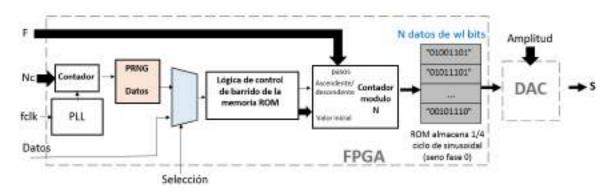

De este modo, se decidió usar la segunda alternativa ya que permite un uso menor de recursos en la placa FPGA. Por otro lado sobre el avance del proyecto se incorporó una entrada de datos externos que, mediante un pulsador desde la FPGA, permite conmutar entre esta y el generador de datos pseudoaleatorios que funciona internamente como se puede observar en la **figura 2.4**. Por su parte también se agregó desde la FPGA una selección de frecuencias y cantidad de períodos de señal por cada dato que aparece.

Figura 2.4: Cambio de fase con selección de datos

### Capítulo 3

# Proyecto

### 3.1. Primera etapa: Circuito implementado en FPGA

El circuito desarrollado en la FPGA mediante el lenguaje de descripción de hardware VHDL (Very High-Speed Integrated Circuit Hardware Description Language), se observa nuevamente en la **figura 2.4**. En la misma se muestran las entradas de selección que permiten variar los parámetros de la modulación. A diferencia de lo que se mencionó en la **sección 2.1** al almacenar solo un cuarto de la señal sinusoidal, la FPGA entrega al DAC las muestras de la señal modulada a una frecuencia fs y 4.N serán la cantidad de muestras de un ciclo de portadora. Por lo tanto el período de portadora resulta Tc=4.N.Ts y el tiempo de dato a transmitir Tb=Nc.4.N.Ts, siendo Ts=1/fs.

El circuito posee una lógica de control que se encarga de establecer si el contador que recorre la memoria realiza una cuenta ascendente o descendente, el valor inicial de esta cuenta y los pasos de incremento/decremento. También determina si el valor extraído de la memoria debe ser negado o no, esto es para determinar el semiciclo positivo o negativo de la señal portadora. Por ejemplo, cuando se desee entregar un período senoidal a la mínima frecuencia de salida, se leerá la memoria de la siguiente forma:

- 1. Cuenta ascendente de 0 a N-1, en pasos de 1.

- 2. Cuenta descendente de N-1 a 0, en pasos de 1.

- 3. Cuenta ascendente de 0 a N-1, en pasos de 1 y salida negada.

- 4. Cuenta descendente de N-1 a 0, en pasos de 1 y salida negada.

Esto genera 4.N muestras de un ciclo de portadora, a la mínima frecuencia posible, que es  $f_c = f_s/(4.N)$ . En esta implementación se tomaron N=256 datos por cuarto de ciclo, es decir 1024 muestras por ciclo. Esta gran cantidad de muestras permite una amplia variación de la frecuencia de portadora a la salida. Es por eso que la máxima frecuencia de portadora estará dada cuando se lean solo 2 muestras por período (variación de la frecuencia de salida mediante saltos entre muestras) teniendo en cuenta una frecuencia  $f_c$  como se muestra en la **ecuación 3.1**, según el teorema de Nyquist.

$$f_c = \frac{f_s}{2} \tag{3.1}$$

En la figura 3.1 se muestra cómo sería la lectura de la memoria de tamaño N para la generación de un ciclo de portadora completo. La entrada de selección determina si los datos modulantes son generados internamente mediante un PRNG, que en este caso se trata de un LFSR (Linear Feedback Shift Register) o se reciben de forma externa.

Figura 3.1: Lectura de memoria de tamaño N para la generación de un ciclo de portadora

#### 3.1.1. Bloques del proceso

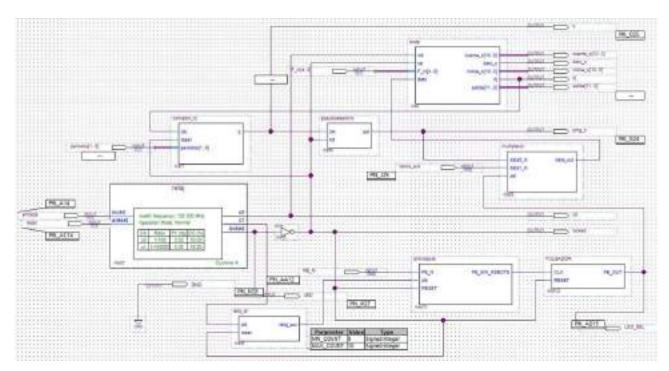

En la figura 3.2 se puede observar el diagrama de los distintos bloques que componen la implementación desarrollada en lenguaje VHDL, que representa el circuito diseñado en la FPGA, y que en este caso se utilizó una placa Cyclone III (Altera) [5] como se observa en la figura 3.3.

Figura 3.2: Diagrama en bloques de la implementación en FPGA

A continuación se irán describiendo cada uno de los bloques de modo sintético y como se relacionan con el resto de bloques funcionales. El circuito completo con cada bloque constitutivo se encuentra en un repositorio GIT [6].

El bloque denominado **onda** posee cuatro entradas y cinco salidas. Una de sus entradas **clk** está conectada a la salida c0 del bloque **reloj** quien provee la señal de reloj necesaria, en este caso la frecuencia máxima será de 1,25MHz, es decir 100 veces menor que la entregada por la FPGA. Este valor de frecuencia máxima esta determinado por el propio diseño de la FPGA y la placa DAC. Así experimentalmente se obtuvo de efectuar diferentes mediciones con el prototipo de la placa DAC, de manera que la señal de salida se comporte como una señal sinusoidal no distorsionada. Por su parte el código prevé una entrada de reset (rst) que proviene también del **reloj**.

Posee una entrada denominada dato por donde ingresan los datos binarios provenientes del bloque pseudo-aleatorio o bien en forma externa. Esta entrada está conectada directamente a la salida  $dato_-o$ . Por su parte este bloque tiene una entrada que denominada  $F_-in$  donde ingresan palabras de 5 bits, que permiten variar la frecuencia de la señal modulada. En la **figura 3.4a** los switches SW3 al SW7, son los encargados de generar tal variabilidad en sus combinaciones del (00000 al 11111). En la **tabla 3.1** se muestran algunas combinaciones de switches para la variación de frecuencia

Figura 3.3: FPGA Cyclone III - Altera

| Switches (F <sub>in</sub> ) | Frecuencia   |  |

|-----------------------------|--------------|--|

| S7 S6 S5 S4 S3              | $\mathbf{F}$ |  |

| 00000                       | 1            |  |

| 00001                       | 2            |  |

|                             |              |  |

| 11110                       | 31           |  |

| 11111                       | 32           |  |

Cuadro 3.1: Variación de frecuencia mediante la combinación de switches en la placa FPGA

Como se mencionó anteriormente, se guardará en la memoria ROM 256 puntos correspondiente a un cuarto de sinusoidal (1023 para la sinusoidal completa a la frecuencia mas baja), cuyos puntos se obtuvieron mediante la discretización de una señal senoidal generada en el programa Matlab, para valores que van de 0 a 2047, que corresponden a 11 bits en potencias de 2. Se trabajará en complemento a 2 (con un bit de signo), se tendrá una salida en el rango de -2048 a 2047, es decir 12 bits que será la resolución del DAC BA9221 elegido para la conversión. El proceso de generación de la señal sinusoidal se describe en la sección 3.1. Tanto  $indice_{-o}$  como  $cuenta_{-o}$  son salidas que se generan mediante el incremento con la señal interna F que es la conversión a número entero de la entrada  $F_{-in}$  mas 1, es decir la combinación  $F_{-in}=00000$  será F=1 y  $F_{-in}=11111$  será F=32. Cuando la  $cuenta_{-o}$  es mayor a 1023,  $indice_{-o}$  toma el valor de la actualización del dato de entrada, de manera de poder mantener su fase actual o bien rotarla 180 grados, objeto fundamental del presente proyecto. Por último rlj es una señal de salida binaria de sincronismo que funciona como señal de reloj del bloque  $contador_{-r}lj$ . Esta señal cambia antes de que  $cuenta_{-o}$  llegue a su valor máximo prefijado, de manera que el dato de entrada esté disponible antes de que se genere un nuevo período de la señal modulada, y se genere un sincronismo entre el dato y inicio de la señal sinusoidal con la fase correspondiente.

El siguiente bloque es el pseudoaleatorio el cual posee una entrada de reloj (clk) conectada a la salida del bloque  $contador\_rlj$ , una entrada de reset (rst) proveniente del bloque reloj y una salida binaria (PRNG). Este bloque tiene la función de generar una señal binaria que funcione como señal de modulante de la señal portadora almacenada en la memoria ROM tal como se describió en el bloque onda.

El comportamiento de este código responde al de un registro de desplazamiento de retroalimentación lineal (LFSR) el cual tiene cargada una palabra de 8 bits como condición inicial y luego va haciendo un desplazamiento hacia la derecha con operaciones intermedias entre bits mediante el uso del operador XNOR.

Con esta aleatoridad, por cada pulso de reloj, se obtiene la señal binaria de salida, tomando el ultimo bit de la palabra formada.

El bloque *multiplexor* posee tres entradas, una de ellas proveniente de la salida del bloque *pseudoaleatorio* (*PRNG*), la otra es una entrada de datos externos (*datos\_ext*) proveniente de un pin de conexión desde la placa DAC, los cuales ingresan hacia la FPGA, debidamente asignado el pin correspondiente. Este multiplexor tiene como función, mediante una entrada de *selección*, conmutar entre la señal pseudoaleatoria interna y una señal externa tal como se mencionó. La entrada de selección proviene de la salida del bloque *PULSADOR*.

La FPGA posee bloques embebidos con distintas funcionalidades los cuales pueden ser instanciados mediante el Quartus II, tal como lo es ALTPLL (Phase-Locked Loop de Altera) quien permite utilizar uno o más señales de reloj estables con las que funciona esta implementación.

El bloque *reloj* el cual es un PLL que genera salidas de clock a partir de la proveída por la placa FPGA, posee dos entradas, una de ellas *(entrada)* representa la máxima frecuencia de la placa, correspondiente a los 125MHz. La otra entrada es un reset sincrónico *(reset)* debidamente mapeado a uno de los pines de la placa FPGA y su respectivo switch con la que se podrá resetear al resto de los bloques de manera manual.

El bloque onda funciona con la señal de reloj de salida  $c\theta$ . Se agregó un segundo reloj, c1, conectado a la entrada de reloj del bloque  $reloj\_ar$ .

Este bloque tiene una salida *locked*. Esta, una vez que el PLL se estabilice, quedará en estado alto. Se conectó un LED en la placa DAC, como testigo del correcto funcionamiento de este bloque, con su correspondiente asignación de pin. Por otra parte, mediante la conexión con una compuerta NOT se uso la condición mencionada como la señal de reset hacia los distintos bloques.

Uno de los parámetros variables de esta implementación es la cantidad de períodos de la señal portadora por cada dato de señal modulante. Esta función se consiguió agregando el bloque **contador\_rlj** el cual posee tres entradas, dos de las cuales son la señal de reloj (clk) que proviene de la salida rlj del bloque **onda** y la entrada reset proveniente de la salida negada del bloque reloj.

Por la tercer entrada ingresan palabras de 2 bits, que permiten variar la cantidad de períodos de señal portadora por dato (1, 2, 4 y 8 períodos por dato). Su funcionamiento interno responde al de un proceso contador que llega hasta un valor máximo. Esta entrada esta debidamente mapeada en el *pin planner* de Quartus, pudiéndose seleccionar desde la placa FPGA con los switches correspondientes.

En la **figura 3.4a** el SW1 y SW2 en sus combinaciones (00, 01, 10, 11) son los encargados de dar variabilidad a la cantidad de períodos de señal.

La salida q de este bloque será la señal de reloj del bloque pseudoaleatorio.

El bloque  $reloj\_ar$  tiene dos entradas, una de ellas la de reloj (clk) y la otra de reset. La primera se encuentra conectada a la señal de reloj c1 del bloque PLL  $(bloque\ reloj)$  cuya frecuencia es de 1250Hz.

Este bloque funciona como un contador con el objetivo de generar una división en frecuencia, 20 veces menor que la frecuencia c1 mencionada. La salida de este bloque  $(reloj\_out)$  será la entrada de reloj del bloque AN-TIRREBOTE.

Seguido al bloque anterior nos encontramos el bloque **ANTIRREBOTE**, quien tiene la función de filtrar los pulsos indeseados que se producen al accionar el pulsador *USER\_PB0* (**figura 3.4a**) mapeado en la FPGA correspondiente a una de sus entradas de datos, *PB\_N*. Sus otras dos entradas son *clk* y *RESET*.

El hecho de que la frecuencia de la señal de salida del bloque anterior sea de 1250Hz, se justifica en el hecho que este bloque necesita una frecuencia de reloj mucho menor (período mas lento) para filtrar el ruido que se producen por el rebote del pulsador *USER\_PB0*.

Internamente funciona desplazando 3 bits de una palabra de 4 bits hacia la derecha, sustituyendo el bit más significativo por la negación lógica del dato leído en el pulsador, de manera de tomar una decisión por comparación, del valor binario que colocará en la salida PB\_SIN\_REBOTE.

El último bloque PULSADOR posee dos entradas, una de ellas clk que es la señal que recibe del bloque anterior y una entrada RESET. Su funcionamiento principal es la de mantener constante la señal de que recibió desde ANTIRREBOTE. Su salida irá conectada a un LED (LED0) la placa FPGA como se puede observar en la (figura 3.4b). Al encenderse indicará que la placa está recibiendo datos externamente, y apagado, mediante los datos aleatorios de forma interna. Esta señal de salida  $(PB\_OUT)$  será la señal de entrada al multiplexor.

(a) Switches y pulsadores

(b) LEDS

Figura 3.4: Switches, pulsadores y leds de la FPGA

### 3.2. Segunda etapa: Circuito conversor digital/analógico

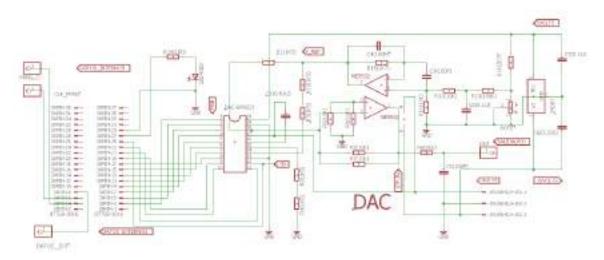

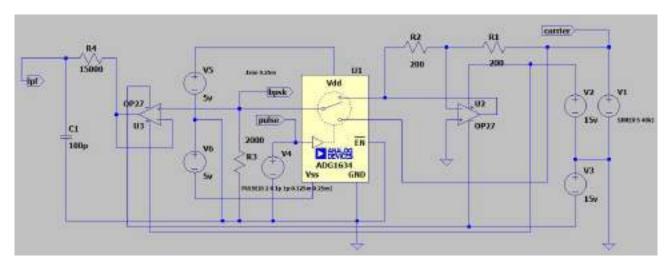

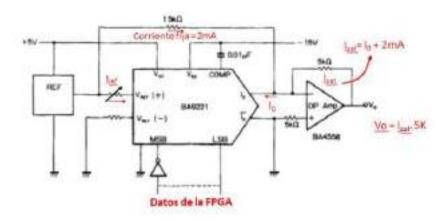

Un esquemático del circuito implementado se muestra en la figura 3.5. Este circuito se encarga de recibir la señal digital de la FPGA y entregar la señal analógica modulada en fase.

El diseño incluye un circuito integrado DAC BA9221 [7], el mismo es un conversor digital-analógico que recibe 12 bits en formato de complemento a dos y entrega una corriente de salida proporcional a una corriente de referencia y a la entrada digital. Este circuito permite variar la corriente de referencia mediante un potenciómetro (POTE en la figura 3.5 mencionada) para obtener distintas amplitudes de la señal de salida, con un máximo de 4 mA como se indica en la hoja de datos.

Luego, esta corriente se convierte a una tensión de 10Volts pico a pico. Esta conversión corriente-tensión, como la capacidad de variar la señal de salida, es posible mediante el uso del circuito integrado NE5532, el cual es un amplificador operacional doble.

El circuito posee una alimentación externa de  $\pm$  15Volts que darán alimentación a ambos circuitos integrados, y una reducción de tensión a 5Volts, mediante un circuito integrado 7805.

Finalmente, un filtro pasabajos se encarga de atenuar las altas frecuencias debidas al ruido de cuantificación.

Figura 3.5: Circuito eléctrico de la placa conversora DAC

El circuito tiene conexión a GND provista por la placa FPGA, debidamente mapeada a uno de sus pines. De los 38 pines que tiene el conector del conversor, solo fueron usados 17, de los cuales 12 corresponden a los bits que ingresan al circuito integrado conversor, 1 corresponde a GND (masa), 1 pin de entrada de datos externos (datos\_ext), 1 pin de salida correspondiente a los datos aleatorios (PRNG\_O), 1 pin de salida llamado PRNG\_CLK que corresponde a la salida q de la figura 3.2, y 1 pin de salida para un conexión de un LED que indica que la señal de salida locked pasó a estado alto. En la FPGA hay una dos pines reservados que se conectan al zócalo conector en la placa DAC que son de reset y la señal de clock, pero que no tiene conexión eléctrica entre placas. El reset se encuentra además mapeado al switch SW1.

#### 3.2.1. Funcionamiento circuital

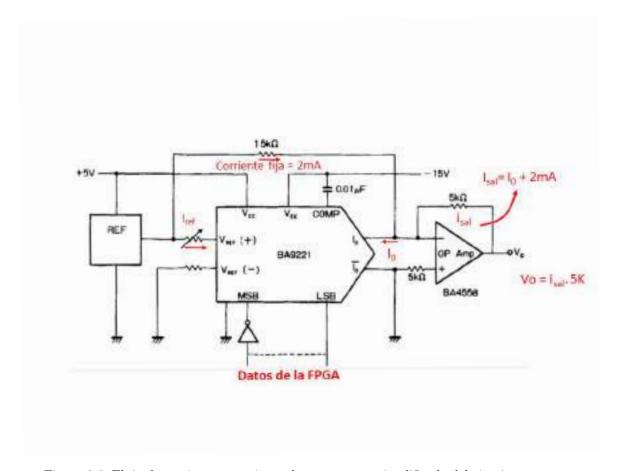

La etapa de conversión D/A se basa en el diseño que provee la hoja de datos del BA9221. Para no variar los valores que recomienda el fabricante, se usaron los pares de resistencias en paralelo R2/R7 y R5/R8 ( $5K\Omega$  en ambos casos), lo mismo que los pares en serie R4/R9 y R10/R3 ( $3K\Omega$  en ambos casos).

Por otra parte el proceso de variación de la tensión de referencia se realiza mediante un divisor resistivo formado por R14 y el potenciómetro (POTE) y una tensión de 5Volts, conjuntamente con el OPAMP en configuración de amplificador no inversor con R15 y R11. Con la **ecuación 3.2** se puede calcular dicha tensión, cuyo cálculo teórico varía entre los valores mínimo y máximo de 0 y 3Volts respectivamente. La corriente de referencia, a full-scale será de 1mA sobre las resistencias en R10 y R3 (ambas de 1k5) en serie.

$$V_{ref} = V_{in} \left( \frac{POTE}{POTE + R_{14}} \right) \left( 1 + \frac{R_{15}}{R_{11}} \right)$$

(3.2)

Desde la FPGA, se debe efectuar la negación del bit mas significativo (MSB) del BA9221 como se indica en la hoja de datos, de manera de poder trabajar correctamente en complemento a dos.

A modo de ejemplo se muestran en la tabla 3.2 los valores que puede tomar la salida de la placa DAC en función de los datos entregados por la FPGA.

| Datos de entrada | Salida analógica |

|------------------|------------------|

| (MSB) / (LSB)    | Vo (Volts)       |

| 011111111111     | 9.9951           |

| 011111111110     | 9.9902           |

| 000000000001     | 0.0049           |

| 000000000000     | 0.0000           |

| 111111111111     | -0.0049          |

| 100000000001     | -9.9951          |

| 100000000000     | -10.0000         |

Cuadro 3.2: Datos de entrada y salida a la placa DAC

En base a este cuadro tomando los casos extremos, a tensión máxima de referencia de 3Volts sobre el par de resistencias en serie que ingresan al pin 14, se obtiene una corriente de referencia máxima de 1mA, de modo que hacia el pin 18 (Io) circulan 2mA por la resistencia de R1 (1k5), esto es cuando los datos de entrada son "01111111111". Los otros 2mA que demanda tal pin, circulan por el par de resistencias R2/R7 desde la salida Vo que se encuentra a aproximadamente 10Volts pico.

Lo explicado aquí puede verse en la **figura 3.6** extraída de la hoja de datos del BA9221 [7], la cual representa un circuito conversor DAC, donde REF representa una fuente de tensión la cual genera una tensión máxima de referencia de 3Volts.

Figura 3.6: Flujo de corriente y tensiones de un esquema simplificado del circuito conversor

Respecto al LED que posee esta placa DAC, se utilizó uno color rojo, los cuales poseen una caída de tensión Vf que oscila entre los 1.8 y 2Volts, que pueden funcionar con corrientes mayores o iguales a los 5mA (If), y que la placa FPGA entrega en sus salidas 2.5Volts (Vs), se optó por utilizar una resistencia en serie  $100\Omega$ , justificando el cálculo con la **ecuación 3.3**, donde se asume el peor caso, cuando Vf es 2Volts.

$$I_f = \left(\frac{V_s - V_f}{R_{led}}\right) = 5mA \tag{3.3}$$

Por otra parte se diseñó un filtro a la salida de la placa DAC del tipo RC pasabajos de primer orden, al que se lo incluyó para atenuar el ruido de cuantificación de alta frecuencia, la cual quedará limitada por el circuito integrado conversor digital analógico (aunque la salida de la FPGA funcione a una frecuencia más alta), que como valor máximo teórico funcionará a 4MHz. Sin embargo experimentalmente para este valor de fs mencionado y previo al filtro, se comprobó deformación de la señal modulada para el valor de F máximo (F=32), por lo que se estableció una fs=1.25MHz. Se debe tener en cuenta que este valor surge propio de las limitaciones de los circuitos integrados usados en su conjunto, no alcanzando los valores teóricos que se mencionan en las hojas de datos.

Como el objetivo principal es dejar pasar la  $fc_{min}$  y  $fc_{max}$  y atenuar el ruido de cuantificación relacionado a la fs, a priori, se estableció la frecuencia de corte del filtro pasabajos, en una década por encima de la máxima frecuencia de la señal modulada  $(fc_{max})$ . Tanto  $fc_{min}$  como  $fc_{max}$ , ambos valores son calculados mediante la **ecuación 3.4** y la **ecuación 3.5** tomando N=1023, fs=1.25MHz, F=1 y F=32 respectivamente.

$$fc_{min} = \frac{F.fs}{N} = 1.22kHz \tag{3.4}$$

$$fc_{max} = \frac{F.fs}{N} = 39.1kHz \tag{3.5}$$

Para justificar el cálculo de la elección de la frecuencia de corte del LPF y el efecto del mismo al aplicarlo, se decide hacer una simulación en el programa LTspice, con un circuito que genera una señal modulada en fase como se observa en la **figura 3.7**.

Figura 3.7: Modulador de fase con ADC1634

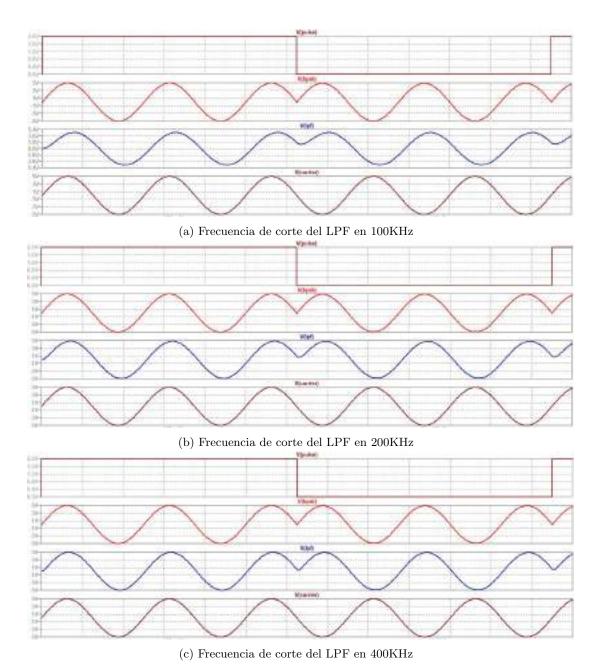

En esta figura se observa un circuito modulador de fase con un generador de pulsos conectado al circuito integrado conmutador ADC1634 [8] el cual conmuta, a la frecuencia del generador de pulsos, una señal senoidal con fase 0 ó fase 180 grados, con el OPAMP OP27 [9] en configuración inversora. Antes del filtro RC, se coloca un circuito operacional seguidor de tensión. En la **figura 3.8** se observa la simulación de este circuito tomando como resistencia R4, los valores de 4k, 8k y 16k y un capacitor C1 de 100pF para ver el efecto del filtro sobre la

señal senoidal a las diferentes frecuencias de corte del mismo, en este caso 400kHz, 200kHz y 100KHz respectivamente. En la misma figura, también se pueden ver la señal cuadrada (modulante) y la senoidal (portadora) mencionadas. La amplitud de la señal senoidal es de 5Volts a una frecuencia de 40KHz, como una aproximación de la  $fc_{max}$ .

Figura 3.8: Señales para la modulación en fase de a diferentes frecuencias de corte del LPF

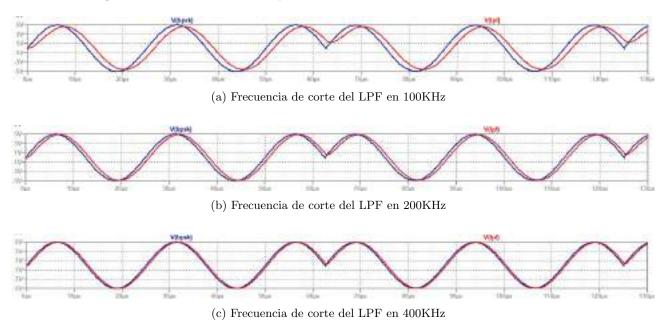

En la figura 3.9 se observan las simulaciones de la señal antes y después del filtro de manera superpuestas para obtener un mayor detalle de comparación. Del análisis de las señales se interpreta que, dentro de la banda de paso, cuanto mas cerca esté la frecuencia de la señal de salida de la frecuencia de corte del filtro, mayor será la atenuación, suavización y atraso en fase de la misma señal antes del filtro. Por el contrario cuanto más lejos, habrá menos atenuación, menos corrimiento en fase y menor será la suavización de la señal, pero se logrará que la señal filtrada este próxima al valor cero de amplitud. Esto sirve de referencia ó proyección para el cálculo definitivo de la frecuencia de corte del filtro, pero se debe tener en cuenta que en esta implementación la modulación se genera de un modo diferente que el realizado en la simulación.

Figura 3.9: Señales para la modulación en fase de a diferentes frecuencias de corte del LPF

Lo que sucede en la práctica, en lo implementado en la FPGA, es que si la frecuencia de corte se encuentra una década por encima de la máxima frecuencia de la señal modulada  $(fc_{max})$ , no se atenúa considerablemente el ruido de cuantificación, y por el contrario si está muy próxima, se atenúa en sus valores pico y donde hay cambio de fase.

Se debe tener en cuenta que la señal portadora no modulada, vista en el espectro, es una señal delta y la portadora modulada, tiene ciertas componentes espectrales que son propias de la modulación. Por su parte el filtro al atenuar ó eliminar las componentes espectrales de la señal modulada, produce el efecto de redondeo o suavización de los saltos de fase.

Cuanto más cerca se encuentre la frecuencia de corte del filtro de la máxima frecuencia de la señal modulada, más se redondean los saltos de fase, más se atenúa en su amplitud pico y mayor atraso en fase. En este caso, mayor es la atenuación del ruido de cuantificación. Así mismo cuanto más lejos, menor atraso en fase, menor atenuación de los saltos en fase y menor atenuación de la amplitud pico. En este caso se produce una menor atenuación del ruido de cuantificación.

Por lo tanto existe una relación de compromiso, donde se busca que la frecuencia de corte se ubique de tal forma que permita pasar a la señal modulada, a la frecuencia más alta  $fc_{max}$ , con suficientes componentes espectrales, y que a su vez no sea tan alta para lograr atenuar el ruido de cuantificación. En otras palabras, tener una frecuencia de corte alta, respecto de la  $fc_{max}$ , que a su vez elimine o atenúe el ruido de cuantificación, con el factor adicional de que no se produzca una excesiva atenuación en los saltos en fase ni en su valor pico de la modulación.

Se decidió experimentalmente tomar valores de componentes tales de estar ligeramente por debajo de la década por encima mencionada, de modo cumplir con lo descripto.

El valor de la resistencia R6 adoptada, es de 5k6 y el capacitor C2 de  $100 \mathrm{pF}$ , y cuyo cálculo se muestra en la **ecuación 3.6**.

$$f_{corte} = \frac{1}{2\pi R_6 C_2} = 284, 2kHz \tag{3.6}$$

Para esta frecuencia, la señal se mantiene en los valores pico a pico de amplitud requeridos y se encuentran suavizados los puntos donde se producen los cambios de fase en la señal modulada, es decir se produce atenuación del ruido de cuantificación. Sin embargo en estos puntos no se llega al valor cero en amplitud de la salida después del filtro.

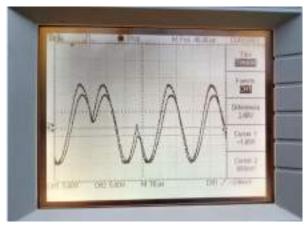

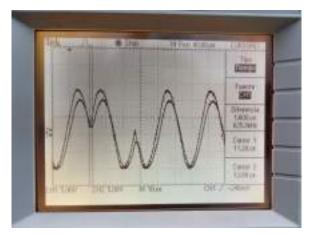

En la figura 3.10 se muestra la señal modulada antes y después del filtro. En la figura 3.10b se aprecia el atraso de fase de la señal tomada en la salida del filtro y la suavización de la misma en los puntos donde hay cambio de fase, que a su vez genera que la señal no llegue a amplitud cero, propio del efecto del mismo filtro en su frecuencia de operación. La diferencia de amplitudes para el caso de frecuencia mínima es de 1Volts y de 2.4Volts para el caso de frecuencia de salida máxima.

Por otra parte en la figura 3.10c se observa la diferencia de fase entre la señal antes y después del filtro, de  $1.6\mu s$  aproximadamente a frecuencia máxima  $(fc_{max} = 39.1kHz)$ . Para la frecuencia de salida mínima  $(fc_{min} = 1.22kHz)$  la señal se encuentra prácticamente en fase antes y después del filtro como se observa en la figura 3.10a.

(a) Amplitudes antes y después del filtro a frecuencia mínima  $1.22 \mathrm{kHz}$

(b) Amplitudes antes y después del filtro a frecuencia máxima  $39.1 \mathrm{kHz}$

(c) Diferencia de fase antes y después del filtro a frecuencia máxima  $39.1 \mathrm{Khz}$

Figura 3.10: Señal modulada antes y después del filtro

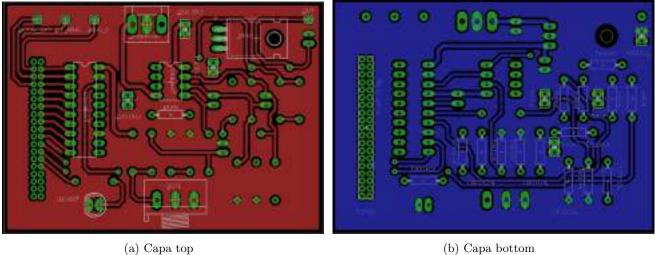

#### 3.2.2. Diseño de la placa

Se tomaron en cuenta dos opciones al momento de elegir el amplificador operacional, en este caso el propuesto por la hoja de datos del conversor BA9221, el cual sugiere el uso del BA4558 [10] y el circuito integrado NE5532 [11]. Este último posee un mayor ancho de banda (BW=10MHz), se encuentra disponible comercialmente y mayor valor de slew rate . Este último parámetro es fundamental para la elección del OPAMP y debe ser mayor que el módulo de la derivada respecto del tiempo de la señal de salida en la componente de mayor frecuencia y para la máxima amplitud. Para este OPAMP según su hoja de datos, el slew rate es de  $9V/\mu s$

Lo expresado queda justificado en las siguientes ecuaciones:

$$V_0(t) = V_0.\sin(\omega_{max}t) \tag{3.7}$$

$$V_0 = 10Volts (3.8)$$

$$\omega_{max} = 39.1KHz \tag{3.9}$$

$$\frac{dV_0(t)}{dt} = \omega_{max}.V_0.cos(\omega_{max}t), \tag{3.10}$$

$$t = 0s (3.11)$$

$$\left| \frac{dV_0(t)}{dt} \right| = \omega_{max} \cdot V_0 = \frac{2.46V}{\mu s} < \frac{9V}{\mu s},$$

(3.12)

Si bien el valor de la frecuencia de portadora máxima con la que estamos trabajando (1,25MHz) es suficiente para cumplir los requerimientos, es importante aclarar que el uso de otro amplificador operacional de mayor ancho de banda, podría dar la posibilidad de aumentar esta frecuencia.

Sin embargo también se debe tener en cuenta la velocidad de datos máxima del BA9221, que es de 4MHz (t=250ns), lo que puede limitar etapas posteriores. Así mismo se realizaron pruebas en protoboard que arrojaron que al modular para el caso de mayor frecuencia (F=32), con estos valores teóricos, no es posible reproducir una señal que mantenga la forma sinusoidal requerida. Por esta razón se optó por bajar la frecuencia de portadora a 1.25MHz.

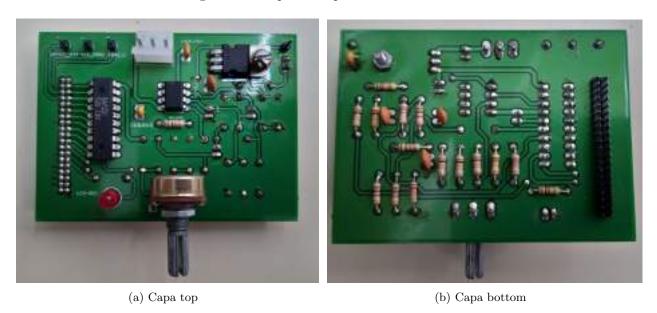

Los encapsulados del conversor y OPAMP son DIP20 y DIP8 respectivamente. El resto de los componentes usados, fueron resistencias de 1/4 de watts, capacitores cerámicos, potenciómetro lineal, led rojo de 5mm, regulador con encapsulado TO220, conector molex de 38 pines y conectores molex de 1 y 3 pines para datos y alimentación respectivamente.

El software elegido para el diseño del conversor, fue el Eagle en su versión 7.6. Se tuvieron en cuenta criterios para la eliminación de capacidades parásitas y se implementó el uso de plano de masa. En la figura 3.11 se muestran las capas top y bottom cada una con su máscara de componentes y antisoldante.

La placa DAC fue realizada por una empresa privada dedicada a tal fin. Fue hecha en material epoxi FR4 de 1.6mm de espesor, con máscara antisoldante verde y serigrafía blanca para la máscara de componentes. El espesor de las pistas de cobre es de 38um, con terminación superficial de estaño sin plomo. El tamaño de la placa es de 61.9x85.07mm con diseño true hole.

En la figura 3.12 se puede observar la placa con sus componentes ensamblados.

(b) Capa botton

Figura 3.11: Capas de la placa conversora DAC

Figura 3.12: Placa conversora DAC - Montaje de componentes

Por último se analiza la posibilidad de incorporar un disipador para el CI7805. Al medir el consumo máximo del mismo, se obtiene que entrega una corriente próxima a los 10mA. La diferencia entre la tensión de entrada y salida es de 10Volts ya que se ingresa con 15Volts y tiene como salida 5Volts. Por lo tanto la potencia a disipar será de 0,1Watts.

Utilizando, la **ecuación 3.13** asumiendo que la temperatura de juntura del dispositivo (Tj) es de 50 °C, la temperatura de ambiente (Ta) de 25 °C, y la resistencia térmica juntura-ambiente  $R\theta ja$ , es de 65 °C/w según la hoja de datos, se obtiene la potencia teórica que se disiparía bajo estas condiciones.

$$P = \frac{T_j - T_A}{R_{\theta j a}} = 0.385 Watts$$

(3.13)

Como el valor de potencia disipada medida es inferior a la potencia calculada, se decide no incorporar un disipador a la placa para este dispositivo el cual será asegurado a la misma mediante una sujeción metálica.

Para el consumo de potencia total del circuito se recomienda consultar el Apéndice E.

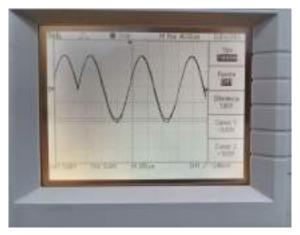

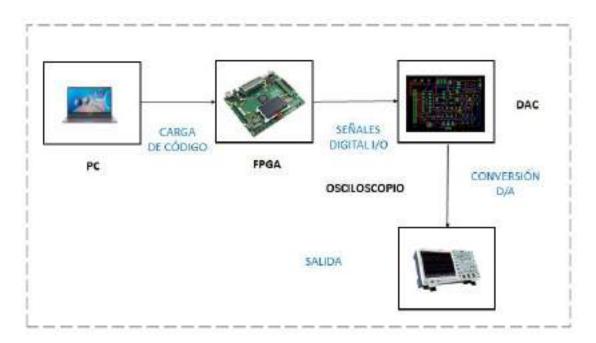

### 3.3. Integración y testeos

El diseño generado en Quartus II, en lenguaje VHDL [6] se carga a la placa FPGA mediante la opción programmer. La placa DAC debe estar conectada en el zócalo del PFGA, alimentada con la fuente dual correspondiente.

La salida de la placa DAC debe estar conectada a uno de los canales del osciloscopio. Con el otro canal se podrán observar el reloj del PRNG y el mismo PRNG interno.

El potenciómetro (POTE) permite modificar la señal de referencia del BA9221, variando así la amplitud pico a pico de la señal de salida.

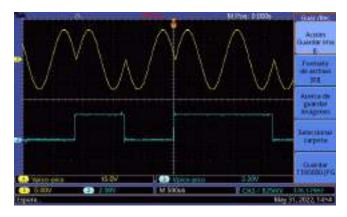

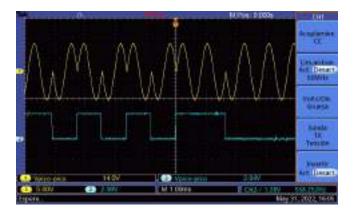

En las **figura 3.13** y **3.14** se observa en el canal 1 la señal modulada tomada desde la salida OUT y en el canal 2 los datos obtenidos de la salida PRNG\_O tomando diferente base de tiempo en el instrumento.

Figura 3.13: Señal modulada de salida y señal de datos PRNG - Base de tiempo  $500\mu s$

Figura 3.14: Señal modulada de salida y señal de datos PRNG - Base de tiempo 1ms

Las dos mediciones se tomaron con una tensión de referencia menor, por lo que se ve en ambas figuras que la tensión de pico a pico es de 15Volts. Esto se hizo con el fin de mostrar tal variación y de poder visualizar sin superposición ambas señales. En las figuras también es de destacar el sincronismo que existe entre ambas señales, donde los datos están disponibles al inicio de un nuevo ciclo de señal.

Lo obtenido condice con la **ecuación 3.5** tomando F = 1, es decir la frecuencia de la señal modulada es de 1,221kHz que corresponde a la frecuencia más baja que se puede obtener.

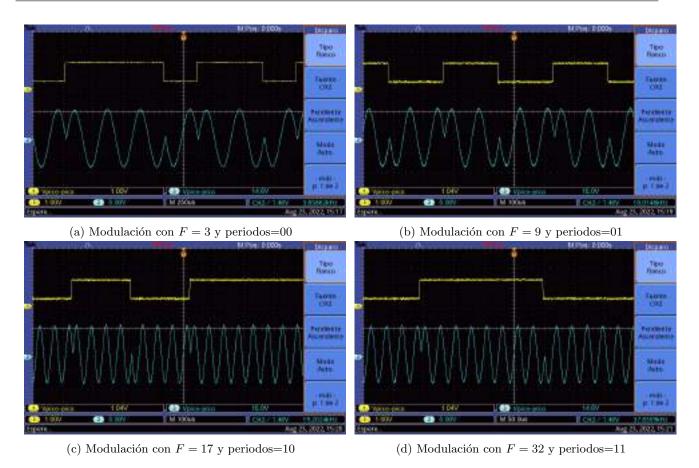

En la figura 3.15 se pueden observar cuatro mediciones para diferentes valores de F y cantidad de ciclos de la señal de entrada (periodos) por cada dato que aparece de la señal modulante. Estas mediciones se tomaron a modo de ejemplo ya que existen más combinaciones para tales parámetros.

Figura 3.15: Mediciones para diferentes parámetros de entrada

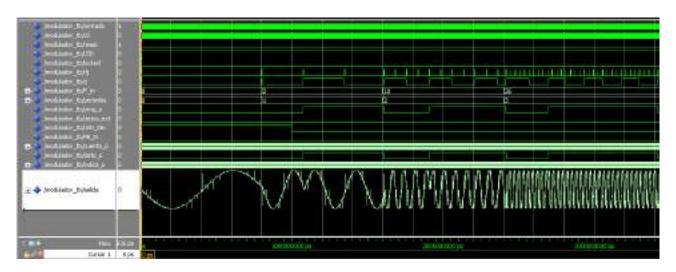

En la figura 3.16 realizada en Model Sim se puede observar todas las señales que intervienen en el diseño, para diferentes parámetros de entrada. Se puede ver como al variar la entrada  $F_{-}in$  cambia la frecuencia de portadora. También se varió la cantidad de ciclos por dato.

Figura 3.16: Simulación realizada en ModelSim para diferentes parámetros de entrada

### Capítulo 4

### Conclusiones

#### 4.1. Resultados finales

En este trabajo se diseñó e implementó un generador de señal modulada en fase. El diseño implementado permite variar los parámetros de la señal modulada de salida como la frecuencia de portadora, potencia de salida, cantidad de ciclos por dato y seleccionar la utilización de datos en forma interna o externa.

La cantidad de recursos empleados en la FPGA es mínimo gracias a la utilización de una memoria que almacena un cuarto de ciclo sinusoidal la cual es leída mediante una lógica de control para generar la señal de portadora. También se diseñó e implementó la placa que recibe la señal digital y entrega la señal analógica, la cual permite variar la potencia de salida de la misma, leer los datos pseudoalatorios generados internamente y su señal de reloj, e ingresar una señal externa en uno de sus periféricos.

En la **Tabla 4.1** se muestran los recursos empleados en una FPGA Cyclone III de Altera para el circuito implementado. Se puede ver que, a pesar de almacenar un gran número de muestras de portadora, consume muy pocos recursos gracias al diseño desarrollado.

| Elementos lógicos (EL) totales (119.088) | 655    |

|------------------------------------------|--------|

| Combinacional de EL                      | 518    |

| Registros de EL                          | 44     |

| Registros dedicados(121.673)             | 137    |

| PLL                                      | 1      |

| $f_{Max}[{ m MHz}]$                      | 181,62 |

Cuadro 4.1: Recursos empleados en la implementación utilizando una FPGA Cyclone III de Altera.

El diseño propuesto admite una frecuencia máxima de operación (fs) de 181,62 MHz lo que permitiría una máxima frecuencia de portadora de 90,81 MHz, y una mínima de 177 kHz.

Las simulaciones hechas tanto con ModelSim y SignalTap de Quartus II como así también las de Matlab, fueron corroboradas mediante las mediciones correspondientes en el osciloscopio, hechas sobre las salidas de la placa DAC tanto en su prototipo montado en protoboard como la placa definitiva. Así mismo las pruebas en protoboard o la placa definitiva, no tuvieron diferencias en cuanto a las mediciones de ruido.

Los cálculos teóricos tuvieron un margen de error tolerable. Para el caso de la tensión de referencia del DAC que debía estar en entre los 0 y 3Volts, con las resistencias comerciales disponibles, se logró combinarlas de tal manera que se llega a una variación de entre 0 y 2,94Volts. Sin embargo el CI7805 por cuestiones tecnológicas, entrega tensión levemente superior los 5Volts, compensándose tal diferencia, situación aceptada ya que se consigue el mismo resultado

El fabricante del CI BA9221 en su hoja de datos, informa que la salida del mismo, a condiciones máximas de Vref, entrega 10 Volts pico a pico. Sin embargo experimentalmente se obtiene 11Volts pico a pico. De todos modos esto no genera una desventaja para esta implementación.

Por último, el potenciómetro lineal utilizado, en su punto de giro mas bajo, no llegó a los  $0\Omega$ , lo que generó que a la salida de la placa DAC haya un mínimo valor de tensión no deseada, pero que sin embargo no genera una condición desventajosa al proceso en general.

### 4.2. Experiencias de la gestión del proyecto

Una de las mayores dificultades asumidas, fue el aprendizaje del leguaje VHDL y el manejo del Quartus II. Con lo primero que se comenzó a trabajar fue en la segunda alternativa de diseño donde finalmente se decidió guardar en memoria un cuarto de la señal sinusoidal, para la reconstrucción completa y para su modulación que, a priori, aún no se contaba con el código correspondiente para generar datos internamente.

Otra singularidad en esta implementación, fue el sincronismo entre cada uno de los bloques que la componen. Fue hasta la última instancia en la elaboración de cada uno de los bloques y la escritura de sus códigos, donde los datos se estaban tomando fuera de tiempo, y que fue solucionado gracias a la señal rlj del bloque **onda** y el bloque **contador\_rlj**.

Sobre el avance del proyecto se agregaron funciones como variación de cantidad de periodos de señal por aparición de dato, bloque antirrebote y multiplexación entre una señal de datos interna o externa.

Por otra parte, se tuvo que reforzar las técnicas de uso del programa Eagle con el que se desarrollo la placa DAC. En principio se pensó en hacerla simple faz, sin embargo el área de la misma era grande y se optó por una doble faz, lo que demoró el diseño definitivo. Previo a esto hubieron dos demoras en el diseño, la primera fue que se pensó en hacer la conexión entre placas mediante cable plano, pero cuestiones de potenciales apariciones de fuentes de ruido, se termino desestimando. La segunda, una mala orientación de los componentes que generarían ya construida, no poder conectarla a la placa FPGA ya que los componentes de ambas placas se tocarían entre sí.

Otro inconveniente surgido fue la excesiva cantidad de calor disipado por parte del CI7805. En un primer momento se utilizaron capacitores electrolíticos para su polarización correspondiente, sin embargo esto fue un error ya que a la frecuencia a la que trabajamos los mismos se encontraban oscilando generando un sobrecalentamiento del dispositivo. La mala implementación no fue detectada rápidamente, y como alternativa se adquirió un modulo tipo flyback el cual funcionaba correctamente. Finalmente se encontró la solución, con el agregado de capacitores cerámicos para el correcto uso del CI7805.

Por último en el transcurso del armado del prototipo de la placa, hubieron dos inconvenientes: el primero fue la incorrecta conexión de pines de salida, que en vez de conectar del MSB al LSB, se lo hizo en sentido contrario no dando la señal de salida esperada. El segundo inconveniente fue que el BA9221, necesita que el MSB se encuentre negado para poder efectuar correctamente el complemento a dos, por lo que se procedió a hacerlo desde el bloque **onda**. Es de destacar, que inicialmente, no estuvo claro como funcionaba la conversión del BA9221. A partir de este punto, se generó una sinergia entre lo que se pretendía tanto en lo referido a código, como lo referido a hardware, y el proyecto avanzó con mayor celeridad.

Como trabajos a futuro, la placa DAC podría ser utilizada como placa conversora de un sistema que funcione con otro tipo de modulación como por ejemplo ASK, FSK ó cualquier otra modulación digital. Algunos bloques pueden ser reutilizados como son los bloques PLL, Antirrebote y el MUX.

Se adquirieron muchos conceptos y técnicas nuevas, y se reforzaron otros. Los tiempos de cada etapa se pueden observar en el plan de proyecto del **Apéndice A**. La experiencia es sumamente gratificante y enriquecedora, desde lo académico como lo humano. Este proyecto fue presentado en el Congreso Argentino de Sistemas Embebidos (CASE 2022) y fue catalogado como trabajo destacado.

### Capítulo 5

# Bibliografía

- [1] Y. Arjoune y N. Kaabouch, «A comprehensive survey on spectrum sensing in cognitive radio networks: Recent advances, new challenges, and future research directions,» Sensors (Switzerland), vol. 19, n.º 1, 2019, ISSN: 14248220. DOI: 10.3390/s19010126.

- [2] A. K. Chaudhary, P. Pratik, S. Gupta y V. Kakkar, «Improved digital design of BPSK modulator using look-up table technique,» en 2013 International Conference on Advances in Computing, Communications and Informatics (ICACCI), IEEE, 2013, págs. 47-52.

- [3] S. Popescu, A. Gontean y G. Budura, «BPSK system on Spartan 3E FPGA,» en 2012 IEEE 10th International Symposium on Applied Machine Intelligence and Informatics (SAMI), IEEE, 2012, págs. 301-306.

- [4] Y. Chye, M. Ain y N. M. Zawawi, «Design of BPSK transmitter using FPGA with DAC,» en 2009 IEEE 9th Malaysia International Conference on Communications (MICC), IEEE, 2009, págs. 451-456.

- $[5] \quad \text{ALTERA, } \\ \text{``ip-basesuite.html,'} \\ \text{`$http://www.altera.com/products/ip/design/basesuite/ip-basesuite.html., 2008.} \\$

- [6] M. Morel, GitHub, GitHub repository, 2022. dirección: https://acortar.link/2RpRLF%20(accedido% 20el%201%20de%20julio%20de%202022)..

- [7] BA9221. dirección: http://www.synfo.nl/datasheets/BA9221.pdf.

- [8] ADC1634. dirección: https://www.analog.com/media/en/technical-documentation/data-sheets/adg16341.pdf.

- [9] OP27. dirección: https://pdf1.alldatasheet.com/datasheet-pdf/view/48504/AD/OP27.html.

- $[10] \quad BA4558. \ dirección: \ \texttt{https://pdf1.alldatasheet.com/datasheet-pdf/view/36012/ROHM/BA4558.} \\ \quad \texttt{html}$

- [11] NE5532. dirección: https://pdf1.alldatasheet.com/datasheet-pdf/view/17968/PHILIPS/NE5532. html.

# Apéndices

# Apéndice A Plan de Proyecto

#### DISEÑO E IMPLEMENTACIÓN DE GENERADOR DE SEÑAL BPSK CON PARÁMETROS REGULABLES

29-ago-2022

http://

Encargado del proyectoMARIANO MORELFechas de inicio y fin del proyecto03-may-2021 - 16-sep-2022

Progreso

99%

Tarea

29

Recursos

3

#### 1. VISIÓN GENERAL

El laboratorio de Procesos Caóticos de la Facultad de Ingeniería de la UNMdP (directores del proyecto) propone la realización de una implementación en FPGA de señales moduladas, que será llevado a cabo para uso de experimental con sensores espectrales de radio cognitiva y servirá además como proyecto final para el desarrollador del mismo. Para eso se propone dos etapas: la programación del código que generará la señal modulada y como hardware, el diseño y fabricación de la placa que servirá como conversor de dicha señal.

#### 2. ALCANCE

El proyecto, en cuanto al software comenzará con el desarrollo de una etapa que genere una señal modulada internamente o externamente, sincronizada y que pueda variar su frecuencia y sus ciclos de repetición sobre un mismo dato. En cuanto al hardware, sobre una placa doble faz se pide poder variar amplitud de referencia, que permita obtener señales de salida y/o ingresar señales de entrada, y hacer la conversión digital-analógica correctamente filtrada. Aprobadas todas las etapas por los directores del proyecto y presentado el proyecto al responsable de la asignatura, se pide la elaboración del informe para su aprobación y presentación final. Se estima la realización del mismo en el transcurso de un año calendario, pero podrán ocurrir retrasos propios de la complejidad de las etapas, o bien para la optimización de actividades ya realizadas.

#### 3. OBJETIVOS

- •Como se mencionada, uno de los objetivos es el desarrollo de la implementación para uso del laboratorio para uso

- experimental para una aplicación específica.

•El otro objetivo es que tal desarrollo permita obtener el título de grado de ingeniero electrónico por parte del interesado quien llevará a cabo el mismo.

- 4. ROLES Y RESPONSABILIDADES

•Mariano Morel: desarrollará cada una de las partes del proyecto y sus modificaciones, como así también la redacción del informe final y su presentación

- •Directores del Proyecto: explicarán los lineamientos del proyecto al desarrollador, aclararán dudas específicas sobre cuestiones técnicas, facilitarán material, darán retroalimentación de las etapas avanzadas e indicarán cuando una etapa quedó concluida. Se encargarán del presupuesto del proyecto.

- •Responsable de la asignatura: recibirá y evaluará el proyecto. Podrá sugerir modificaciones. Se encontrará en contacto con los directores del proyecto y con el desarrollador del mismo.

#### 5. ENTREGABLES

A modo general se harán tres entregas específicas a los directores del proyecto •Finalización del código que ejecutará la FPGA

- •Finalización del diseño y armado de la placa conversora

- •Entrega de resultados é informe final (a directores y responsable de la asignatura)

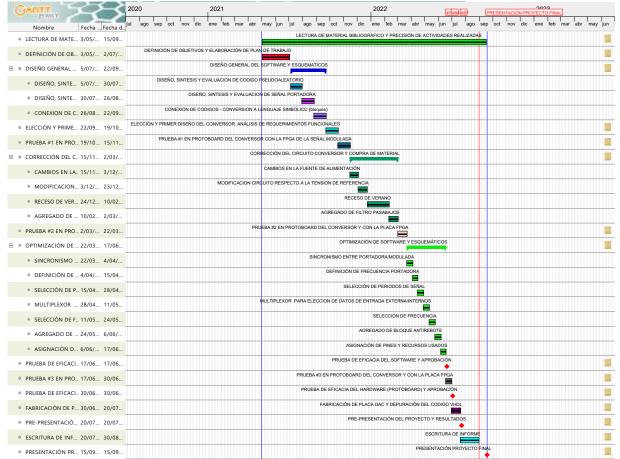

6. CALENDARIO Se elaborará un cronograma y recursos con el que visualizarán los avances (Diagrama de Gantt)

7. PRESUPUESTO

El costo de materiales e insumos para realizar el proyecto será costeado con fondos asignados al laboratorio mencionado, no teniendo injerencia en el mismo el desarrollador.

| rea                                                                                                                                                                                                                                                                                                                                                                                                              |                 |              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|

| Nombre                                                                                                                                                                                                                                                                                                                                                                                                           | Fecha de inicio | Fecha de fin |

| LECTURA DE MATERIAL BIBLIOGRAFICO Y PRECISIÓN DE ACTIVIDADES<br>REALIZADAS                                                                                                                                                                                                                                                                                                                                       | 3/05/21         | 15/09/22     |

| Esta actividad comprende el aprendizaje continuo de conceptos y técnicas para el desarrollo de este proyecto, y la potencia modificación y optimización que se deban realizar por pedido o por el simple avance aspectos no tenidos en cuenta inicialmente o sobre el mismo desarrollo por el avance propio de todas las actividades. El porcentaje de avance puede tener fluctuaciones y podría ser modificado. |                 |              |

| DEFINICIÓN DE OBJETIVOS Y ELABORACIÓN DE PLAN DE TRABAJO                                                                                                                                                                                                                                                                                                                                                         | 3/05/21         | 2/07/21      |

| Para esta actividad, mediante una comunicación fluida con los directores del laboratorio de procesos caóticos, se definieron los aspectos más relevantes que debe contener el proyecto. Las modificaciones y retroalimentación se harán en cada una d las actividades                                                                                                                                            | е               |              |

| DISEÑO GENERAL DEL SOFTWARE Y ESQUEMATICOS                                                                                                                                                                                                                                                                                                                                                                       | 5/07/21         | 22/09/21     |

| Esta actividad es fundamental ya que en este momento se comienza a trabajar en lenguaje VHDL sobre el programa Quartu. Il, y se elaboran los códigos, que luego serán simulados y representados en forma esquemática: el código pseudoaleatorio y la señal portadora, que juntas serán las modulación generarán la modulación esperada.                                                                          | is<br>'         |              |

| DISEÑO, SINTESIS Y EVALUACION DE CODIGO PSEUDOALEATORIO                                                                                                                                                                                                                                                                                                                                                          | 5/07/21         | 30/07/21     |

| DISEÑO, SINTESIS Y EVALUACION DE SEÑAL PORTADORA                                                                                                                                                                                                                                                                                                                                                                 | 30/07/21        | 26/08/21     |

| CONEXION DE CODIGOS - CONVERSION A LENGUAJE SIMBOLICO (bloques                                                                                                                                                                                                                                                                                                                                                   | ) 26/08/21      | 22/09/21     |

| ELECCIÓN Y PRIMER DISEÑO DEL CONVERSOR. ANÁLISIS DE<br>REQUERIMIENTOS FUNCIONALES                                                                                                                                                                                                                                                                                                                                | 22/09/21        | 19/10/21     |

| En esta actividad se elige el modelo circuital y componentes que harán la conversión digital - analógica, en concordancia co los requerimientos del software y de la placa FPGA.                                                                                                                                                                                                                                 | n               |              |

| PRUEBA #1 EN PROTOBOARD DEL CONVERSOR CON LA FPGA DE LA SEÑAL<br>MODULADA                                                                                                                                                                                                                                                                                                                                        | _ 19/10/21      | 15/11/21     |

| En esta actividad se arma un prototipo del circuito y se prueba el correcto funcionamiento de la señal de salida (conversión), variación de la tensión de referencia respecto de la salida, la correcta conexión de de los pines de datos, alimentaciones y ruido.                                                                                                                                               | la              |              |

| CORRECCIÓN DEL CIRCUITO CONVERSOR Y COMPRA DE MATERIAL                                                                                                                                                                                                                                                                                                                                                           | 15/11/21        | 2/03/22      |

| En esta actividad se define:                                                                                                                                                                                                                                                                                                                                                                                     |                 |              |

| -Componentes y modelo de fuente de alimentación a usar<br>-Se incorpora un nuevo modelo de circuito para variar la tensión de referencia<br>-Se agrega un filtro RC pasabajos                                                                                                                                                                                                                                    |                 |              |

| CAMBIOS EN LA FUENTE DE ALIMENTACIÓN                                                                                                                                                                                                                                                                                                                                                                             | 15/11/21        | 3/12/21      |

| MODIFICACION CIRCUITO RESPECTO A LA TENSION DE REFERENCIA                                                                                                                                                                                                                                                                                                                                                        | 3/12/21         | 23/12/21     |

| RECESO DE VERANO                                                                                                                                                                                                                                                                                                                                                                                                 | 24/12/21        | 10/02/22     |

| rea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |              |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------------|--|

| Nombre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Fecha de inicio | Fecha de fin |  |

| AGREGADO DE FILTRO PASABAJOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 10/02/22        | 2/03/22      |  |

| PRUEBA #2 EN PROTOBOARD DEL CONVERSOR Y CON LA PLACA FPGA Se realiza una nueva prueba teniendo en cuenta la primera prueba y las modificaciones planteadas en la actividad anterior. Se analizan los resultados                                                                                                                                                                                                                                                                                                                                                                                                                              | 2/03/22         | 22/03/22     |  |

| OPTIMIZACIÓN DE SOFTWARE Y ESQUEMÁTICOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22/03/22        | 17/06/22     |  |

| Esta actividad comprende la optimización de lo ya realizado con respecto al software. Algunas de ellas son propias de una<br>necesidad que surgió en forma posterior a la idea original o bien porque no fue posible desarrollar una actividad con las<br>técnicas usadas o por alguna limitación tecnológica                                                                                                                                                                                                                                                                                                                                |                 |              |  |

| -se sincronizaron todas bloques funcionales -se agregó la función que posibilita variar la frecuencia de la señal desde switchs ubicados en la placa FPGA -se agregó un bloque que permite modificar la cantidad de periodos por dato -se incorporó un multiplexor para poder ingresar datos en forma externa mediante un pulsador que además cuenta con una mejora antirrebote -se definió la frecuencia maxima de portadora -se asignarón pines a la FPGA desde el programa Quartus para su correcto funcionamiento al conectarlo a la placa conversora -se analizaron la cantidad de recursos consumidos por el software en la placa FPGA |                 |              |  |

| SINCRONISMO ENTRE PORTADORA/MODULADA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22/03/22        | 4/04/22      |  |

| DEFINICIÓN DE FRECUENCIA PORTADORA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4/04/22         | 15/04/22     |  |

| SELECCIÓN DE PERIODOS DE SEÑAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15/04/22        | 28/04/22     |  |

| MULTIPLEXOR PARA ELECCION DE DATOS DE ENTRADA EXTERNA/INTERNOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28/04/22        | 11/05/22     |  |

| SELECCIÓN DE FRECUENCIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11/05/22        | 24/05/22     |  |

| AGREGADO DE BLOQUE ANTIREBOTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24/05/22        | 6/06/22      |  |

| ASIGNACIÓN DE PINES Y RECURSOS USADOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6/06/22         | 17/06/22     |  |

| PRUEBA DE EFICACIA DEL SOFTWARE Y APROBACIÓN Los directores del laboratorio dan aprobada lo que respecta al software, mediante una prueba definitiva.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17/06/22        | 17/06/22     |  |